【电子行业标准(SJ)】 半导体集成电路 Jμ320C25-40、Jμ320C25-50型数字信号处理器详细规范

本网站 发布时间:

2024-07-05 02:15:27

- SJ50597.12-1994

- 现行

- 点击下载此标准

标准号:

SJ 50597.12-1994

标准名称:

半导体集成电路 Jμ320C25-40、Jμ320C25-50型数字信号处理器详细规范

标准类别:

电子行业标准(SJ)

标准状态:

现行-

发布日期:

1994-09-30 -

实施日期:

1994-12-01 出版语种:

简体中文下载格式:

.rar.pdf下载大小:

581.88 KB

手机扫码下载更方便

点击下载

标准简介:

标准下载解压密码:www.bzxz.net

SJ 50597.12-1994 半导体集成电路 Jμ320C25-40、Jμ320C25-50型数字信号处理器详细规范 SJ50597.12-1994

部分标准内容:

中华人民共和国电子行业军用标准FL 5962

ST 50597.12--- 94

半导体集成电路

Jμ 320C25-40、Jμ 320C25-50型数字信号处理器详细规范

Detail specification for type Jμ 320C25-40.Jμ 320C25-50 digital signal processorsof semiconductor integrated circuits1994-09-30发布

1994-12-01实施

中华人民共和国电子工业部批准中华人民共和国电子行业军用标准半导体集成电路Jμ320C25:40、Jμ320C25一50型数字信号处理器详细规范Detait specification for type J-320C25--4DJμ320c25--50digilalsignalprocessorsof semiconductor inlegrated circuils1范围

1.1 主题内容

SJ 50597. 12--94

空规范规定了毕导体集成电路Jμ320C25—40.J1320C25—50型数宇信号处理群(以下箭称器件)的洋细要求。

1.2活用范围

本规范造用于器件的研制、生和采购。1.3分类

本规范对微电路按器件型号、器件等级、封装形式、额定值和推荐工作条件来分类。1.3.1器件缔号

器件编号应按GB597微电路总规范》第3.6.2条的规定。1.3.1.1器件型号

器件型号如下:

碧件型号

Jμ320C25—43

J32:c25--5

1.3.1.2器件等级

器件等级应为GJB59?第3.4条规的B级利态规范规楚的B1级。本规范中未对B级另加说明的条款理解为与B级杆同。1.3-1.3封装形式

封装形式妥GB7092半哥仁集成自路外形尺>的规定封装形式如下:

中华人民共和国电子工业部

封装形式

心68P3(陶瓷针栅阵列封装)

Q68P3(陶瓷四面引线扇平封装)C68P3(陶瓷无引线片式载位封装)1994-09-30发布

199-1-12-01实施

-rKAONKAca-

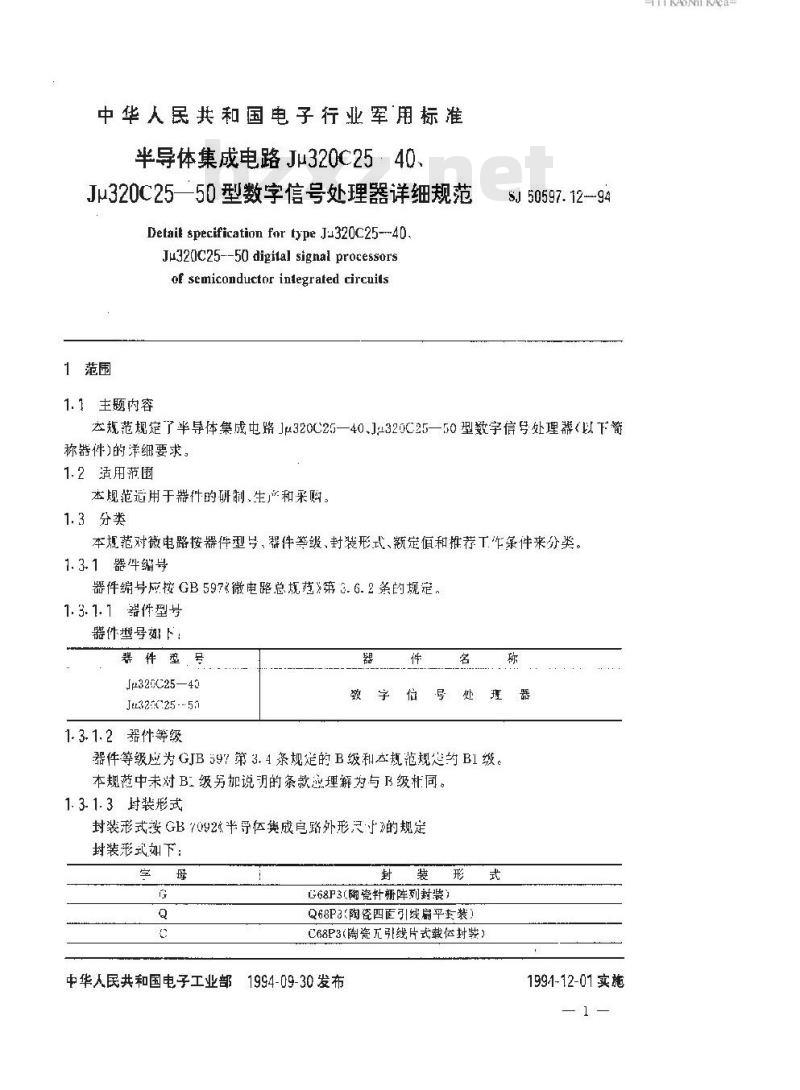

1.3.2绝对最大额定值

绝对最大额定值如下,

狂一引+端柜对于Vss端电压

驴存温嵌范市

引线耐焊接温度(1s)

1.3.3推荐工作条件

推荐T作条件妇下:

电源电

输八富电半电压

输人低屯

平电压

工作频率

Ju32cC25--10

Jp3225-55

M~D15.FSX

SJ 50597. 12--94

J320c2

Jm32GC.25—5n

CPP/CPX

民输人

DU~D.5.FSX.CPIN.CPX.CPR

兵它输人

320C25—4n

523C25-—50

输出低中平勺流

输出高电平司流

引用文件

GB3431.286

GB 4590--84

GB 7C92

GJB 546—88

GJB 597---88

GJB 1649—93

SJ/2 90.5.2—87

半导医集成电路文字符号引出端功能符号半导体集成自路机械和气候试验方法半导体集成自路外形尺寸

微电子器件试险方法和程序

微电路总规范

电子产品防静电放电控制大纲

辛导体器件集成电路

第2部分:数字集放电路

-- 300

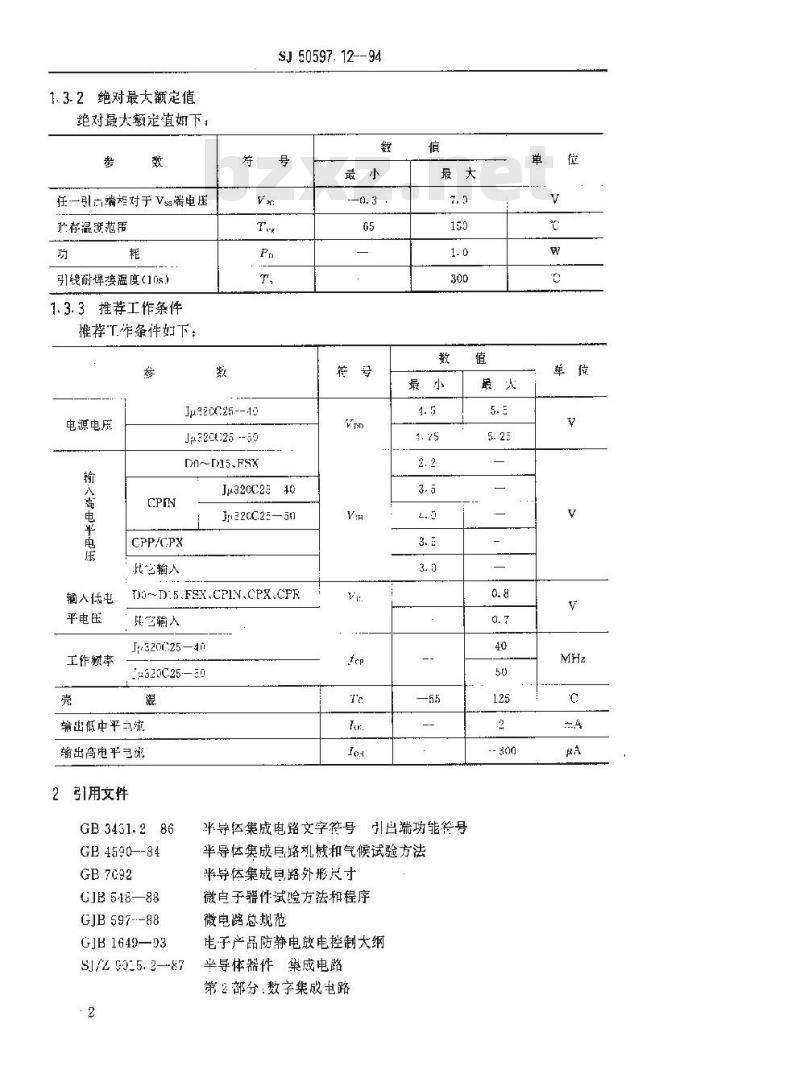

3要求

3.1详细要求

SJ 50597. 1294

各项要求应按GJB597和本规范的规定3.2设计、结构和外形尺寸

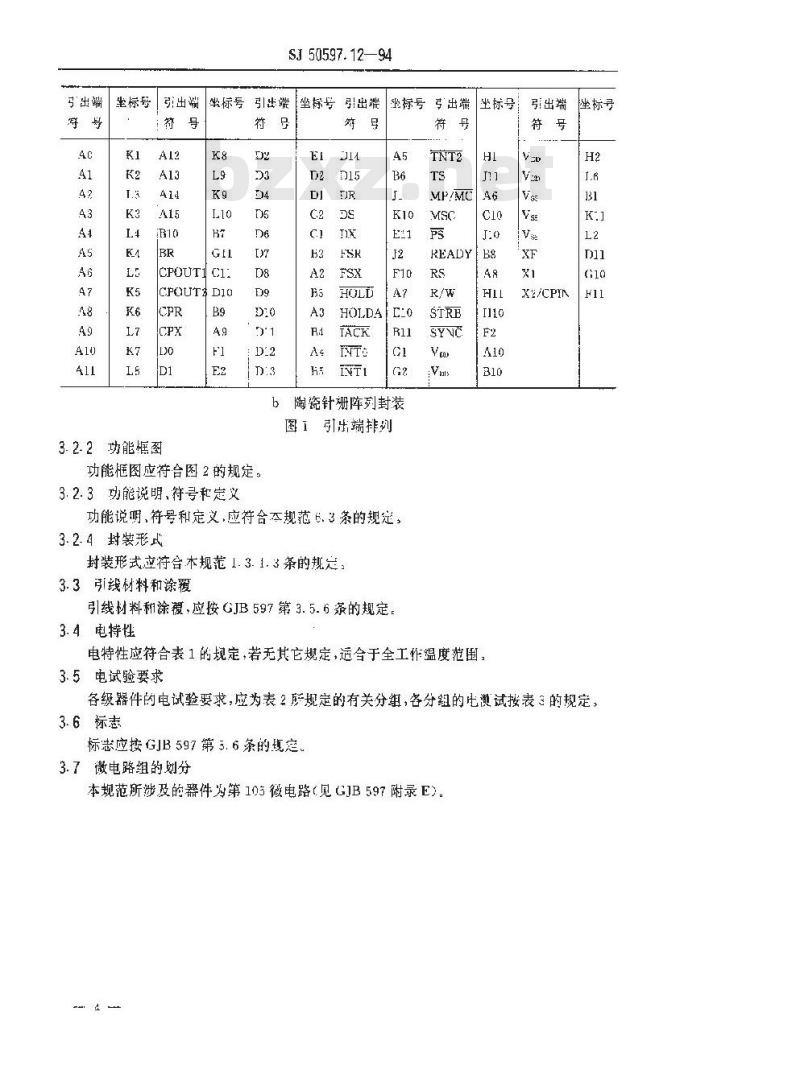

设计、结构和外形尺寸应符合GJB537和.本规范的规定3:2.1引出端排列

引出端排列应符合图1的规定。引出端排列为俯视医。杭

8 83888elI##NSY

9 8 7 6 3 4 3 216867666564636261Nsshi0

05 h 13

04 6 14

02 5 15

INT621

TNT2 6 22

Yep623

FS# 5 25

AG 5 26

60l IAck

S8iCPOUT

57CPOUT2

561 XF

X2/CPIN

27282930313233343536373839404142433101293890919939

陶瓷四面引线扁平封装

陶瓷无引片式载体封装

-TrKAoNiKAca-

垒标号弱出端

SJ 50597.1294

坐标号引出

CPOUTic:

CPOUTA D1O

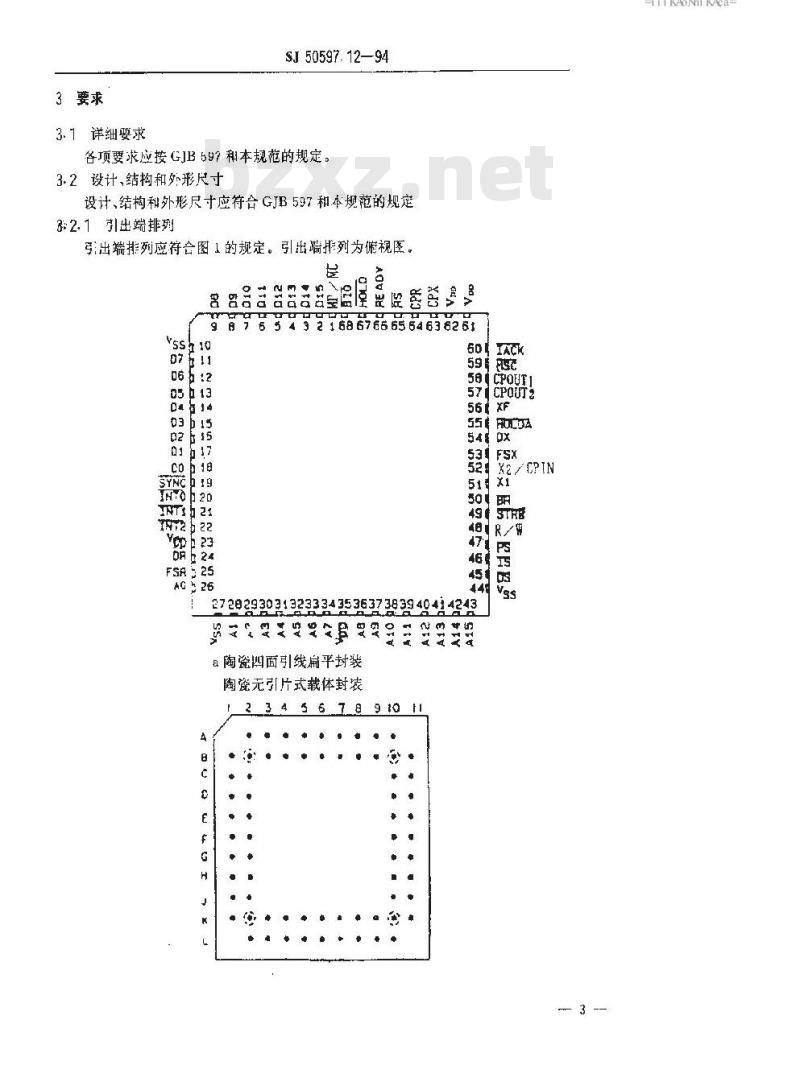

3.2.2功能框图

坐标号引出端

坐标号出端

b陶瓷针珊阵列封装

图1引出端排列

功能框图应符合图2的规定。

3.2.3功能说明,符号和定义

功能说明,符号和定义,应符合本规范6.3条的规定,3.2.4封装形式

封装形式应符合本规范1.3.1.3条的规定:3.3引线材料和涂覆

引线材料和涂覆,应按GJB597第3.5.6条的规定,3.4电持性

坐标号

电特性应符合表1的规定,若无其它规定,适合于全工作温度范围,3.5电试验要求

引出端

X2CPIN

座标号

各级器件的电试验要求,应为表2所规定的有关分组,各分组的比测试按表3的定,3.6标志

标患应接GJB597第5.6条的现定

3.7微电路组的划分

本规范所涉及的器件为第105微电路(见GJB597附录E)。4

115-40

015-p0

MCS116

SJ 50597.12—94

FFC(16)

pe (isn

[4086 X16]

持想:

ARCIFE

XFETT6

AFSTI6I

ARSTTBT

RAU6N (AU

致捆RAM B1块

(256 16)

注;图中的符号意义如

等些量10-16)

来自R的

7个SB

256 461

图2功能图

RPcTer

ASA(61

AR(16)

X(161

PAn(6)

GAE容的]

服序总域

事运器

PA(32)

脉效着 5.0, 4]

ALU R32T

MAGCH6M

ACCLEL

TrKAONKAca-

ACCH-累加器高位

ACCL=累如器低位

ALU-算术罗钜单活

ARA=辅助寄存器算术运算单元

ARR=辅助等存器指针缓油器

ARP=辅助寄存器指针

DP=数据件储誉页指针

DRR=串行Ⅱ数据接收寄存器

DXR申行口数据发送寄存器

[FR=i断标志奇存器

MR-由断屏蔽奇行器

IR一指令寄存器

MCS=微调用难线

QR-双列指令寄存器

PR-慈积奇存器

PRC=周期寄存器

TIM=定时器

TR=暂存器

PC一程序计数露

PFC=预取计数器

RPIC.=错环计数器

GREG一全展产储器分配寄存

RSR-串行L接收移位寄行器

XSR一串行口发送移位寄存器

ARO~AR?继寄存器\卷”

ST0~ST1=状态奇存器

C-进位立

MLX=多路选择器

$J 50597. 12-94

若无其它规定,Tc——55~125C,V-5V±10%(Ju320C25—40),Vpr5V±5%(Ju320C25-5c)Vss=0V序1)

输出高电平电压Vo

输出低电平电压VoL

Tm=—300uA,Vm,=- 4. 5V

U20C2516).

Yuw-4.75V(J:38cC25-55),V,-Vu(最大),VH(最小)

Ju. = 2mA. Vm = . 5V(F±32(C25407

Vm=4:75V(Jμ320C25--5C),V,-Vn(最大),V最小)

规范值

u325C25 40 Jμ320C25-50

输出高电阻态电1u2

输人电流

中演空蒙/HOLI

输入电容

输出电容

输入/愉出电容

翰人对

SJ50597.12—94

续表1

OVsV+VaVon= 5. 5V(Ju32C25

40)VDO=3.25VUu520C25-5C)

OVVVp-5.5V

Vn=5. 5V(Jμ320C25—40)

Vm=5.?5(/321C25-50)

V--lrUm

T:: =250

rojVn-uv

CH>UT1/CPOUT2周期

[CPIN高平到CPOUTCHINH·CR):TIL高电平延退过前

CPIN 高中平到 CP<>UT1 (C小H-Lt:低电平延迟时间

CPIN高电平到CPOUIT2

CNCUTE)

高毛乎延迟对问

CPIN高电平到CPOUT2(CH-CPOU

低电平延逻对司

CPIN高电平到STRE高电ACANH-STERBF平延迟时间

CPIN高电平到STRE低电RH-AR

平延退时间

CPOLT1,CPOUT2,STRA

下降时间

规范俏

J±390C25-40

最小墩太

Te32cC25

J320C25-50

±20 ±4

±10u4

4320C25

TKAONKAca-

CPUUTI、CPOUT2.STRB

上升时间

SJ50597.12--94

续表1

CPUTI,CHOUT2 低电平+w GOUL

CPOUE1,CPOUT2 高电 2w.na 14.来

CPOUTI.CPOL:T2 电F 国n.Ou-CPUT2.钟退时间

EPIN周期时间

PIV 低密,孕脉穿”

CPIN高平脉宽

tierins

CFIN 低中乎前SYNC建立tSSYNET.M:时闻

从CPIN低电平开的SYNC

保持时间

IgUYNCT.-.CI..

thIL.-SY AL:H

认CPOUT1开始STR延时THSTREL

28 CPOL1:到STRB延退时间

d:CCOTR--STRBH:

IH: 't+h stH'h

IIt .Iey SIk

29TRR低电平前地址建立时间214SLREBCSTR高包平后地址保持时间”

STRB低电平脉宽”

32STRB奇巴平脉宽4

tI(STRM.: AN)

we-KRE?

STRB高电平前数据写建立时teUaW-STEEH33

STREB高电平开始数据写保待ISTRH.DX)时间

STR常低电平后数据总线开始 STKHI--V:35

驱动允许时间(写短期)

36STRB高电平后数据总线三态;tdirs-FRF:禁止时间(写周期)

Jp32sC25-40

Jx320C25-50bZxz.net

2Q-3 2Q-82Q-72Q+5 ms

-12Q17ns

2Q—62Q-+82Q

Q-6|Q+6

teemx)

Q+15ns

Q- 4ns

Q--5 Q-6-5

52Q+=2Q52Q--5

5|2Q-+52Q—52Q

SJ 50597. 12-94

续表1

从CPOUT1开始MSC有效延(MSV-CPXUTIHI37

der!..Mar

从地址时间开始读数据存取时AV-Dw,\间

STRB高电平以前效据读建立s

SUUY-RHF

从STRB高中平并始数据读保esTKH-DE持时间

STR日低电平后READY有效(STRHIL--RFANYH)41

延迟时间

42 CPOUT2高电书后 READY 24(COUTSH-RE ADVH)有效建迟时间

STRB低电平READY后保持

实ADYY

CPOUT2高电平启READY TWCROUTY RENYV)保持时间

MSC有效后READY有效延NSCL-RASYL45

返挝间

MSC有效后 READY 保持时

CMSCHREADYII)

47CPOUT1 低中平到进人复位dr:OT-1-Ra,状态延退时期

48CPOLIT1到TACK有效延迟时

STRB下降沿前XF有效时间

TA(CANT:.CKH

IdLACKY-CPOUTIHI

SU 25 CROUT

CPOTI 高电平前INT,BTO,

RS建立时间

ISU:XSH CTH

SUN--L

ACY·CPOLTIR

Ju320C25 40 Ju320C23 50

Q—20

gQ—31 ns

Q—2cn

2Q—2 ne

Q:10

ns12,13,

TKAONKAca

CPOUT1 高电平后NT,BIO

RS保持吋间

INT、BIO低电平脉宽

53R5低电平脉宽

54CPOLIT1低电平后HOIA低

电平时间

55CPOUT1 低电平后地址兰态

禁止时间

56 HOLD高中平到HOLDA高电

评时间

CPOLT1低电平前地址驱动

CPOUT2高电平片HOLD有

效时间”

CPX上升哲后DX有效时间”

[FSX 下降沿后 DX 有效时间

(TXM=0)

61CPX上升沿后FSX有效时间

62率行口频率

串行口时钟(CPX/CPR)陶期

串行口时转(CPX,CPR)周期

审行口时钟(CPX/CPR)低电

平脉宽

串行口时钟(CPX/CPR)高电

平脉宽

CPX/CPR下降哲前 FSX/

FSR 建立时间

68CPX.CPR下降格前FSX/

ESR保持时间

CPR 一降沿前 DR 建立时间

CPR下降措后 DR 保持时间

注:Q=1/4tc

SJ 50597. 12 : 94

续表1

tI:CFOUTH-RSH B

th(EPEUTIH-INTH

E(CUTHO:

Id(CPMIT11HILIAI.:

tainCPUUTU—A2,

AdCHO.TH-HILNAH:

eFA CFOUTAH. HOLDH)

TA(\Pt2hH: In.)

teCFAH--EXV

+dCPXH-FSXH)

+=(CPXH- FEXL>

te:scra

te scre

tnatpe,

tw:scpm:

ES11(FSH H.-C:PRI.)

ZSU(F5H-CPXL)

thLPKL-FHR.)

thCrxL-FEx)

ESUCDRY-OPRL

tbePR1,DRE)

1)本表中参数的序弓与对应波形图中参数的缩导是一致的。规

Jμ320C25-50

Ju320C25-40

2)CPIN的占空系数[tCP—2iCPN:/tca必须在40~60%范图内。10

Q—19

6250kHz

ns 18,19

SJ 50597. 12--94

3)A0--A15、FS,DS,S,STRF、R/W、的时库部可参照“地址\时序包括在该时序中。4) CPOUT1/CPOUT2 边洛剂STRB达沿之间相互眼踪,导致 tW(ETR., 利 IW(E:1:为 2Q 而无等述态。

5) 读数据存取时间定义为trAV--AY)—sUTAV-SIRELI+st(DYSTRBH)+t。) ,INT和BIO为异步输入端,在时钟周期的任何时刻都可能产生。然而,如吴规定的立时间得到横足,则会产生时序图中的焰确时序。TNT、RTC)下降时间必须少于 8。7)FSX下降沿和CPX上升沿的悬后出现。5) 单行口时钟占空系数必须在 10~~6%范围内,中行口时靶上升和下降时,间必须少于 25n3 :9)FOLD为异步输入期,在时钟间期的任何时刻都可能产生,如果规定的建立时间得到满足,则会产生时序图中的精晚时序。另外CPOUT2周期的延遇要发生表2试验要求

若无其它规定,表中采用的试验方法系指GJB 548试验方法。试验要求

中间(老化前)电试验

(方法5004)

最电測试1

(方法5064)

A 粗试验要求\

(方法5005)

B 组 Vzar试验

C 组继点电测试

(方法5005)

C 组检验增加的分组

D 组终点电测试

(方法50G5)

B级器伴

组(见表3)

BJ.级器件

A,A2,A3, A7.A8.A9, A10,

IA:1A2.A3, A4, A7, A8, A9,

见本规范 4.5.3条

A2.A8(仅 125G)A10

不要求

A2,A8(123 仅C),A10

注;1) A1,A7 分组要求 PIA 计算见本范 4. 2 条),2)A4 分组仅用于鉴定(见本规范 4. 4. 1录)。表 3A组电测试

分组序号

Vu4. 5V(Jμ320C25—40)

Vro=4.75V(lμ320C25—50)

LUR=-303AA

V=VL(最大),VH(最则)

A-A2,A3,A7.A9

A1,A2.A3.44,A7.A9

见本效范 4. 5. 3条

A2,A86仅 125 )

A2,A8(仅 125 C)

Tu320C25-

-42u320C25

-TrKAONTKAa-

ST 50597.12--- 94

半导体集成电路

Jμ 320C25-40、Jμ 320C25-50型数字信号处理器详细规范

Detail specification for type Jμ 320C25-40.Jμ 320C25-50 digital signal processorsof semiconductor integrated circuits1994-09-30发布

1994-12-01实施

中华人民共和国电子工业部批准中华人民共和国电子行业军用标准半导体集成电路Jμ320C25:40、Jμ320C25一50型数字信号处理器详细规范Detait specification for type J-320C25--4DJμ320c25--50digilalsignalprocessorsof semiconductor inlegrated circuils1范围

1.1 主题内容

SJ 50597. 12--94

空规范规定了毕导体集成电路Jμ320C25—40.J1320C25—50型数宇信号处理群(以下箭称器件)的洋细要求。

1.2活用范围

本规范造用于器件的研制、生和采购。1.3分类

本规范对微电路按器件型号、器件等级、封装形式、额定值和推荐工作条件来分类。1.3.1器件缔号

器件编号应按GB597微电路总规范》第3.6.2条的规定。1.3.1.1器件型号

器件型号如下:

碧件型号

Jμ320C25—43

J32:c25--5

1.3.1.2器件等级

器件等级应为GJB59?第3.4条规的B级利态规范规楚的B1级。本规范中未对B级另加说明的条款理解为与B级杆同。1.3-1.3封装形式

封装形式妥GB7092半哥仁集成自路外形尺>的规定封装形式如下:

中华人民共和国电子工业部

封装形式

心68P3(陶瓷针栅阵列封装)

Q68P3(陶瓷四面引线扇平封装)C68P3(陶瓷无引线片式载位封装)1994-09-30发布

199-1-12-01实施

-rKAONKAca-

1.3.2绝对最大额定值

绝对最大额定值如下,

狂一引+端柜对于Vss端电压

驴存温嵌范市

引线耐焊接温度(1s)

1.3.3推荐工作条件

推荐T作条件妇下:

电源电

输八富电半电压

输人低屯

平电压

工作频率

Ju32cC25--10

Jp3225-55

M~D15.FSX

SJ 50597. 12--94

J320c2

Jm32GC.25—5n

CPP/CPX

民输人

DU~D.5.FSX.CPIN.CPX.CPR

兵它输人

320C25—4n

523C25-—50

输出低中平勺流

输出高电平司流

引用文件

GB3431.286

GB 4590--84

GB 7C92

GJB 546—88

GJB 597---88

GJB 1649—93

SJ/2 90.5.2—87

半导医集成电路文字符号引出端功能符号半导体集成自路机械和气候试验方法半导体集成自路外形尺寸

微电子器件试险方法和程序

微电路总规范

电子产品防静电放电控制大纲

辛导体器件集成电路

第2部分:数字集放电路

-- 300

3要求

3.1详细要求

SJ 50597. 1294

各项要求应按GJB597和本规范的规定3.2设计、结构和外形尺寸

设计、结构和外形尺寸应符合GJB537和.本规范的规定3:2.1引出端排列

引出端排列应符合图1的规定。引出端排列为俯视医。杭

8 83888elI##NSY

9 8 7 6 3 4 3 216867666564636261Nsshi0

05 h 13

04 6 14

02 5 15

INT621

TNT2 6 22

Yep623

FS# 5 25

AG 5 26

60l IAck

S8iCPOUT

57CPOUT2

561 XF

X2/CPIN

27282930313233343536373839404142433101293890919939

陶瓷四面引线扁平封装

陶瓷无引片式载体封装

-TrKAoNiKAca-

垒标号弱出端

SJ 50597.1294

坐标号引出

CPOUTic:

CPOUTA D1O

3.2.2功能框图

坐标号引出端

坐标号出端

b陶瓷针珊阵列封装

图1引出端排列

功能框图应符合图2的规定。

3.2.3功能说明,符号和定义

功能说明,符号和定义,应符合本规范6.3条的规定,3.2.4封装形式

封装形式应符合本规范1.3.1.3条的规定:3.3引线材料和涂覆

引线材料和涂覆,应按GJB597第3.5.6条的规定,3.4电持性

坐标号

电特性应符合表1的规定,若无其它规定,适合于全工作温度范围,3.5电试验要求

引出端

X2CPIN

座标号

各级器件的电试验要求,应为表2所规定的有关分组,各分组的比测试按表3的定,3.6标志

标患应接GJB597第5.6条的现定

3.7微电路组的划分

本规范所涉及的器件为第105微电路(见GJB597附录E)。4

115-40

015-p0

MCS116

SJ 50597.12—94

FFC(16)

pe (isn

[4086 X16]

持想:

ARCIFE

XFETT6

AFSTI6I

ARSTTBT

RAU6N (AU

致捆RAM B1块

(256 16)

注;图中的符号意义如

等些量10-16)

来自R的

7个SB

256 461

图2功能图

RPcTer

ASA(61

AR(16)

X(161

PAn(6)

GAE容的]

服序总域

事运器

PA(32)

脉效着 5.0, 4]

ALU R32T

MAGCH6M

ACCLEL

TrKAONKAca-

ACCH-累加器高位

ACCL=累如器低位

ALU-算术罗钜单活

ARA=辅助寄存器算术运算单元

ARR=辅助等存器指针缓油器

ARP=辅助寄存器指针

DP=数据件储誉页指针

DRR=串行Ⅱ数据接收寄存器

DXR申行口数据发送寄存器

[FR=i断标志奇存器

MR-由断屏蔽奇行器

IR一指令寄存器

MCS=微调用难线

QR-双列指令寄存器

PR-慈积奇存器

PRC=周期寄存器

TIM=定时器

TR=暂存器

PC一程序计数露

PFC=预取计数器

RPIC.=错环计数器

GREG一全展产储器分配寄存

RSR-串行L接收移位寄行器

XSR一串行口发送移位寄存器

ARO~AR?继寄存器\卷”

ST0~ST1=状态奇存器

C-进位立

MLX=多路选择器

$J 50597. 12-94

若无其它规定,Tc——55~125C,V-5V±10%(Ju320C25—40),Vpr5V±5%(Ju320C25-5c)Vss=0V序1)

输出高电平电压Vo

输出低电平电压VoL

Tm=—300uA,Vm,=- 4. 5V

U20C2516).

Yuw-4.75V(J:38cC25-55),V,-Vu(最大),VH(最小)

Ju. = 2mA. Vm = . 5V(F±32(C25407

Vm=4:75V(Jμ320C25--5C),V,-Vn(最大),V最小)

规范值

u325C25 40 Jμ320C25-50

输出高电阻态电1u2

输人电流

中演空蒙/HOLI

输入电容

输出电容

输入/愉出电容

翰人对

SJ50597.12—94

续表1

OVsV+VaVon= 5. 5V(Ju32C25

40)VDO=3.25VUu520C25-5C)

OVVVp-5.5V

Vn=5. 5V(Jμ320C25—40)

Vm=5.?5(/321C25-50)

V--lrUm

T:: =250

rojVn-uv

CH>UT1/CPOUT2周期

[CPIN高平到CPOUTCHINH·CR):TIL高电平延退过前

CPIN 高中平到 CP<>UT1 (C小H-Lt:低电平延迟时间

CPIN高电平到CPOUIT2

CNCUTE)

高毛乎延迟对问

CPIN高电平到CPOUT2(CH-CPOU

低电平延逻对司

CPIN高电平到STRE高电ACANH-STERBF平延迟时间

CPIN高电平到STRE低电RH-AR

平延退时间

CPOLT1,CPOUT2,STRA

下降时间

规范俏

J±390C25-40

最小墩太

Te32cC25

J320C25-50

±20 ±4

±10u4

4320C25

TKAONKAca-

CPUUTI、CPOUT2.STRB

上升时间

SJ50597.12--94

续表1

CPUTI,CHOUT2 低电平+w GOUL

CPOUE1,CPOUT2 高电 2w.na 14.来

CPOUTI.CPOL:T2 电F 国n.Ou-CPUT2.钟退时间

EPIN周期时间

PIV 低密,孕脉穿”

CPIN高平脉宽

tierins

CFIN 低中乎前SYNC建立tSSYNET.M:时闻

从CPIN低电平开的SYNC

保持时间

IgUYNCT.-.CI..

thIL.-SY AL:H

认CPOUT1开始STR延时THSTREL

28 CPOL1:到STRB延退时间

d:CCOTR--STRBH:

IH: 't+h stH'h

IIt .Iey SIk

29TRR低电平前地址建立时间214SLREBCSTR高包平后地址保持时间”

STRB低电平脉宽”

32STRB奇巴平脉宽4

tI(STRM.: AN)

we-KRE?

STRB高电平前数据写建立时teUaW-STEEH33

STREB高电平开始数据写保待ISTRH.DX)时间

STR常低电平后数据总线开始 STKHI--V:35

驱动允许时间(写短期)

36STRB高电平后数据总线三态;tdirs-FRF:禁止时间(写周期)

Jp32sC25-40

Jx320C25-50bZxz.net

2Q-3 2Q-82Q-72Q+5 ms

-12Q17ns

2Q—62Q-+82Q

Q-6|Q+6

teemx)

Q+15ns

Q- 4ns

Q--5 Q-6-5

52Q+=2Q52Q--5

5|2Q-+52Q—52Q

SJ 50597. 12-94

续表1

从CPOUT1开始MSC有效延(MSV-CPXUTIHI37

der!..Mar

从地址时间开始读数据存取时AV-Dw,\间

STRB高电平以前效据读建立s

SUUY-RHF

从STRB高中平并始数据读保esTKH-DE持时间

STR日低电平后READY有效(STRHIL--RFANYH)41

延迟时间

42 CPOUT2高电书后 READY 24(COUTSH-RE ADVH)有效建迟时间

STRB低电平READY后保持

实ADYY

CPOUT2高电平启READY TWCROUTY RENYV)保持时间

MSC有效后READY有效延NSCL-RASYL45

返挝间

MSC有效后 READY 保持时

CMSCHREADYII)

47CPOUT1 低中平到进人复位dr:OT-1-Ra,状态延退时期

48CPOLIT1到TACK有效延迟时

STRB下降沿前XF有效时间

TA(CANT:.CKH

IdLACKY-CPOUTIHI

SU 25 CROUT

CPOTI 高电平前INT,BTO,

RS建立时间

ISU:XSH CTH

SUN--L

ACY·CPOLTIR

Ju320C25 40 Ju320C23 50

Q—20

gQ—31 ns

Q—2cn

2Q—2 ne

Q:10

ns12,13,

TKAONKAca

CPOUT1 高电平后NT,BIO

RS保持吋间

INT、BIO低电平脉宽

53R5低电平脉宽

54CPOLIT1低电平后HOIA低

电平时间

55CPOUT1 低电平后地址兰态

禁止时间

56 HOLD高中平到HOLDA高电

评时间

CPOLT1低电平前地址驱动

CPOUT2高电平片HOLD有

效时间”

CPX上升哲后DX有效时间”

[FSX 下降沿后 DX 有效时间

(TXM=0)

61CPX上升沿后FSX有效时间

62率行口频率

串行口时钟(CPX/CPR)陶期

串行口时转(CPX,CPR)周期

审行口时钟(CPX/CPR)低电

平脉宽

串行口时钟(CPX/CPR)高电

平脉宽

CPX/CPR下降哲前 FSX/

FSR 建立时间

68CPX.CPR下降格前FSX/

ESR保持时间

CPR 一降沿前 DR 建立时间

CPR下降措后 DR 保持时间

注:Q=1/4tc

SJ 50597. 12 : 94

续表1

tI:CFOUTH-RSH B

th(EPEUTIH-INTH

E(CUTHO:

Id(CPMIT11HILIAI.:

tainCPUUTU—A2,

AdCHO.TH-HILNAH:

e

TA(\Pt2hH: In.)

teCFAH--EXV

+dCPXH-FSXH)

+=(CPXH- FEXL>

te:scra

te scre

tnatpe,

tw:scpm:

ES11(FSH H.-C:PRI.)

ZSU(F5H-CPXL)

thLPKL-FHR.)

thCrxL-FEx)

ESUCDRY-OPRL

tbePR1,DRE)

1)本表中参数的序弓与对应波形图中参数的缩导是一致的。规

Jμ320C25-50

Ju320C25-40

2)CPIN的占空系数[tCP—2iCPN:/tca必须在40~60%范图内。10

Q—19

6250kHz

ns 18,19

SJ 50597. 12--94

3)A0--A15、FS,DS,S,STRF、R/W、的时库部可参照“地址\时序包括在该时序中。4) CPOUT1/CPOUT2 边洛剂STRB达沿之间相互眼踪,导致 tW(ETR., 利 IW(E:1:为 2Q 而无等述态。

5) 读数据存取时间定义为trAV--AY)—sUTAV-SIRELI+st(DYSTRBH)+t。) ,INT和BIO为异步输入端,在时钟周期的任何时刻都可能产生。然而,如吴规定的立时间得到横足,则会产生时序图中的焰确时序。TNT、RTC)下降时间必须少于 8。7)FSX下降沿和CPX上升沿的悬后出现。5) 单行口时钟占空系数必须在 10~~6%范围内,中行口时靶上升和下降时,间必须少于 25n3 :9)FOLD为异步输入期,在时钟间期的任何时刻都可能产生,如果规定的建立时间得到满足,则会产生时序图中的精晚时序。另外CPOUT2周期的延遇要发生表2试验要求

若无其它规定,表中采用的试验方法系指GJB 548试验方法。试验要求

中间(老化前)电试验

(方法5004)

最电測试1

(方法5064)

A 粗试验要求\

(方法5005)

B 组 Vzar试验

C 组继点电测试

(方法5005)

C 组检验增加的分组

D 组终点电测试

(方法50G5)

B级器伴

组(见表3)

BJ.级器件

A,A2,A3, A7.A8.A9, A10,

IA:1A2.A3, A4, A7, A8, A9,

见本规范 4.5.3条

A2.A8(仅 125G)A10

不要求

A2,A8(123 仅C),A10

注;1) A1,A7 分组要求 PIA 计算见本范 4. 2 条),2)A4 分组仅用于鉴定(见本规范 4. 4. 1录)。表 3A组电测试

分组序号

Vu4. 5V(Jμ320C25—40)

Vro=4.75V(lμ320C25—50)

LUR=-303AA

V=VL(最大),VH(最则)

A-A2,A3,A7.A9

A1,A2.A3.44,A7.A9

见本效范 4. 5. 3条

A2,A86仅 125 )

A2,A8(仅 125 C)

Tu320C25-

-42u320C25

-TrKAONTKAa-

小提示:此标准内容仅展示完整标准里的部分截取内容,若需要完整标准请到上方自行免费下载完整标准文档。

标准图片预览:

- 热门标准

- 电子行业标准(SJ)

- SJ/T11376-2007 数字电视接收设备条件接受接口规范 第2-1部分:通用传送接口(UTI)技术规范

- SJ/T31450-1994 氧气输送管道完好要求和检查评定方法

- SJ/T31449-1994 供油管道完好要求和检查评定方法

- SJ/T11138-1997 电缆分配系统用物理发泡聚乙烯绝缘同轴电缆

- SJ/T10148.1-1991 电气简图的编制方法 术语、分类和编制原则

- SJ/T11399-2009 半导体发光二极管芯片测试方法

- SJ/T11403-2009 通信用激光二极管模块可靠性评定方法

- SJ/Z610-73 场致发光荧光粉的试验方法

- SJ/T11377-2007 数字电视接收设备条件接受接口规范 第2-2部分:通用传送接口(UTI)测试规范

- SJ/T31452-1994 水处理设备完好要求和检查评定方法

- SJ50033.129-1997 半导体分立器件 3DD155型低频大功率晶体管详细规范

- SJ/T10795-1996 通用硬同轴传输线及其法兰连接器详细规范

- SJ20978.3-2007 空中交通管制系统监视数据交换规范第3部分:单雷达气象信息传输

- SJ3062.2-1988 冲裁模通用模架 T形槽固定板

- SL/T809—2021 水利对象基础数据库表结构及标识符

- 行业新闻

请牢记:“bzxz.net”即是“标准下载”四个汉字汉语拼音首字母与国际顶级域名“.net”的组合。 ©2025 标准下载网 www.bzxz.net 本站邮件:wymp4wang@gmail.com