- 您的位置:

- 标准下载网 >>

- 标准分类 >>

- 通信行业标准(YD) >>

- YD/T 853-1996 速率高达14400bit/s传真用二线调制解调器的技术要求

标准号:

YD/T 853-1996

标准名称:

速率高达14400bit/s传真用二线调制解调器的技术要求

标准类别:

通信行业标准(YD)

标准状态:

现行-

发布日期:

1996-05-08 -

实施日期:

1996-11-01 出版语种:

简体中文下载格式:

.rar.pdf下载大小:

285.96 KB

手机扫码下载更方便

点击下载

标准简介:

标准下载解压密码:www.bzxz.net

范围:本标准规定速率高达14400bit/s(简称高速)文件传真用的调制解调器的调制方法和操作程序。本标准适用于高速文件传真机的研究、开发和生产,为高速文件传真机的互通提供技术依据。 YD/T 853-1996 速率高达14400bit/s传真用二线调制解调器的技术要求 YD/T853-1996

部分标准内容:

YD/T853—1996

本标准等效采用国际电报电话咨询委员会(CCITT)建议V.17(1991年版本)。用于检测速率高达14400bit/s传真用二线调制解调器本标准由邮电部电信科学研究规划院提出并归口。本标准起草单位:邮电部电信传输研究所。本标准主要起草人:苟雅莉、王新京、崔进水。525

YD/T853-1996

CCITT前言

CCITT(国际电报电话咨询委员会)是国际电信联盟(ITU)的常设机构。CCITT负责技术、操作资费问题的研究,并且为了实现全世界电信标准化,对上述问题发布建议。每四年举行一次的CCITT全体会议确定研究课题,并批准所属研究组提交的建议。在两次全体会议期间CCITT成员对建议的审议是以CCITT2号决议(墨尔本1988)的程序进行的。建议V.17由第17研究组制定,并在1991年2月22日以2号决议的程序被批准。CCITT注

在本建议中,“主管部门”词是指电信主管部门和经认可的私营机构二者的简称526

1范围

中华人民共和国通信行业标准

速率高达14400bit/s传真用

二线调制解调器的技术要求

YD/T853.1996

eqv CCITT V: 17 : 1991

本标准规定速率高达14400bit/s(简称高速)文件传真机用的调制解调器的调制方法和操作程序。本标准适用于高速文件传真机的研究、开发和生产,为高速文件传真机的互通提供技术依据。2引用标准

下列标准所包含的条文,通过在本标准中引用而构成为本标准的条文。本标准出版时,所示版本均为有效。所有标准都会被修订,使用本标准的各方应探讨,使用下列标准最新版本的可能性。CCITTV.24:1988数据终端设备(DTE)和数据电路终接设备(DCE)之间的接口电路定义表3引言

本建议规定了高速传真机应用的调制解调器的调制方法和操作程序。对于传真机传输应用的操作方法和其他特性应参考适当的T系列建议,因为一般传真三类机应用的高速调制解调器的有关建议与本标准有区别。调制解调器的基本特性如下:

a)提供下列数据信号速率下的半双工操作:-14400bit/s同步;

-—12000 bit/s同步;

9600bit/s同步;

-7200bit/s同步。

b)在2400 Bd(波特)下以同步线路传输的正交调幅。c)包括数据扰码器、自适应均衡器和八状态格状编码。d)用于训练和同步的二序列:长训练和再同步。4线路信号

4.1载波频率

信道载波频率是1800Hz士1Hz。接收机在收到载波频率最大偏移为±7Hz的信号时应能工作。4.2调制

调制速率为2400±0.01%Bd。

4.3信号码元编码

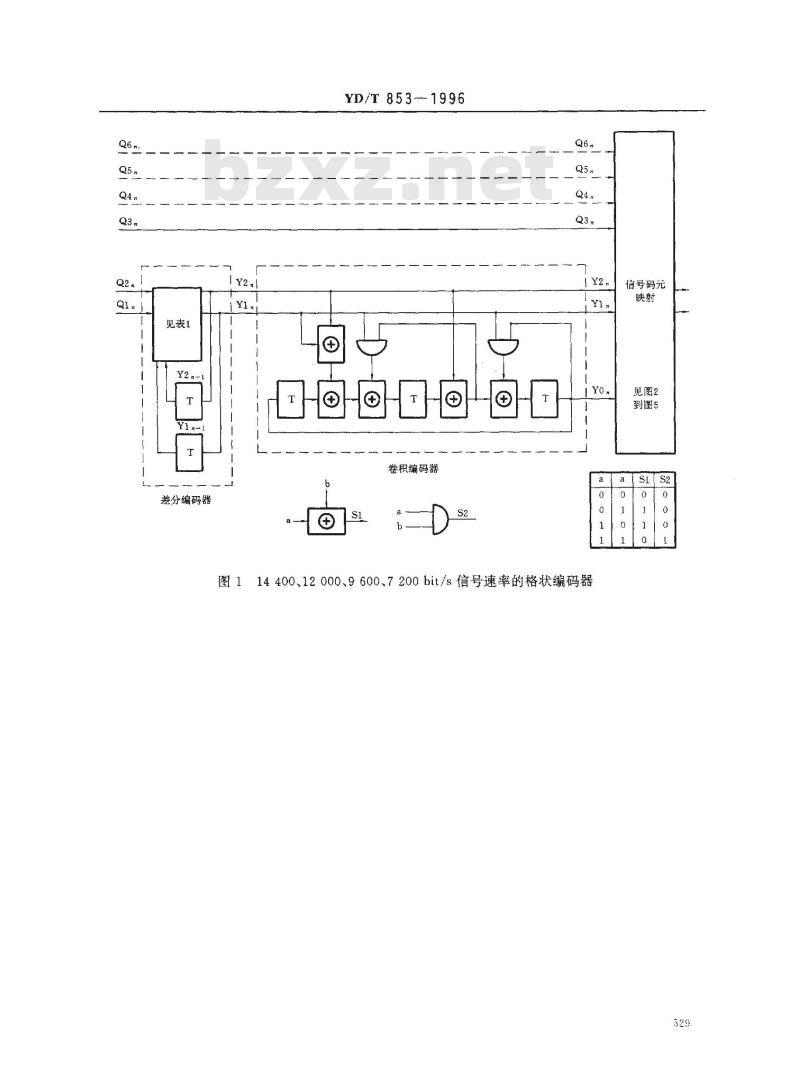

4.3.114400bit/s的信号码元编码经扰码待发送的数据流按6个连续数据比特分为一组,这些数据比特按照其出现的时间排序。如图1所示,每组的前两个比特Q1和Q2(这单n表示该组的序号),按照表1的规定首先差分编码为Y1和Y2元。

中华人民共和国邮电部1996-05-08批准1996-11-01实施

YD/T853—1996

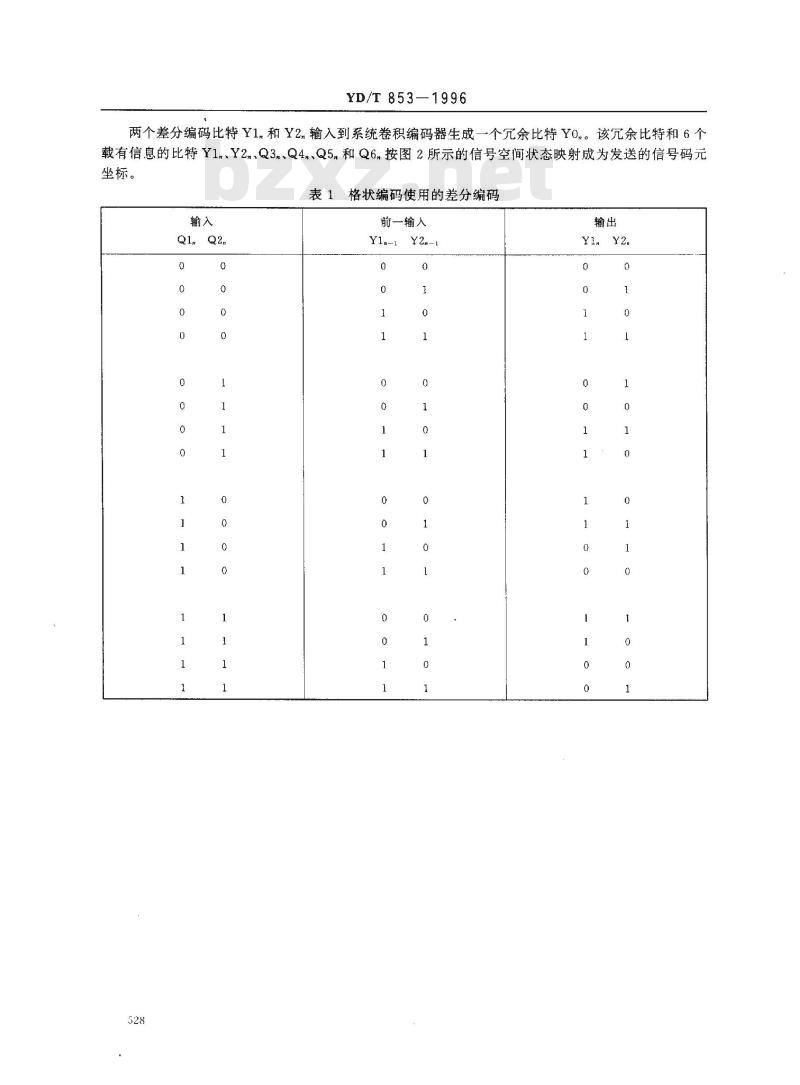

两个差分编码比特Y1.和Y2,输入到系统卷积编码器生成一个亢余比特YO元。该穴余比特和6个载有信息的比特Y1,Y2折,Q3mQ4元、Q5,和Q6%按图2所示的信号空间状态映射成为发送的信号码元坐标。

表1格状编码使用的差分编码

Y1, Y2,

前一输入

见表1

差分编码器

YD/T853---1996

卷积编码器

图114400、12000、9600、7200bit/s信号速率的格状编码器信号码元

见图2

到图5

YD/T 853--1996

0000110

0000011

1100100

1011101

1010110www.bzxz.net

1010011

1000100

0001101

1001111

1001010

1100001

1011000

1101111

1101010

1000001

0001000

0001110

0001011

1110100

1111101

0010110

0010011

0100100

0011101

1110110

-811100m

1001100

0000101

1000111

1000010

1110001

1111000

0101111

0101010

0100001

0011000

1010100

1101101

0011110

0011011

0110100

0111101

0110110

—40110011

-6 1111111

1111010

1001001

0000000

0101100

0010101

1100110

1100011

1010001

1101000

0100111

0100010

0110001

0111000

-2 0111111

0111010

0101001

0010000

1011111

1011010

1011110

1011011

0010100

0101101

0111110

0111011

0111100

0110101

0100110

0100011

1101100

1010101

H00111

1100010

0010001

0101000

0110111

0110010

0111001

0110000

0011111

0011010

1101001

1010000

0000100

1001101

1111011

0011100

0100101

0101110

0101011

1111100

1110101

1000110

1000011

0000001

1001000

1110111

1110010

0011001

0100000

0010111

0010010

0001100

1000101

1101110

1101011

1011100

il11001?

1100101

1110000

0001111

0001010

1001110

1001011

0001001

1000000

1010111

1010010

1011001

1100000

Q000111

0000010

注:二进制数指Q6m、Q5、Q4,、Q3、Y2、Y1n、YOn。A、B.C和D指的是同步信号码元。图214400bit/s数据信号速率下格状编码所使用的128点信号结构4.3.212000bit/s的信号码元编码经扰码待发送的数据流,按5个连续数据比特分为一组,这些数据比特照其出现的时间排序。如图1所示,每组前两个比特Q1,和Q2(这里n表示该组的序号),按照表1规定首先差分编码为Y1,和Y2.

两个差分编码比特Y1,和Y2,输入到系统卷积编码器生成一亢余比特YOn。该穴余比特和5个载有信息的比特Y1、Y2折Q3n、Q4m和Q5按图3所示的信号空间状态图映射成为发送的信号码元坐标。4.3.39600bit/s的信号码元编码经扰码待发送的数据流,按4个连续数据比特分为一组,这些数据比特照其出现的时间排序。如图1所示,每组前两个比特Q1,和Q2,(这里n表示该组的序号),按照表1规定首先差分编码为Y1.和Y2元

两个差分编码比特Y1.和Y2输入到系统卷积编码器生成一亢余比特YO。该余比特和4个载530

YD/T853--1996

有信息的比特Y1,、Y2mQ3,和Q4,按图4所示的信号空间状态图映射成为发送的信号码元坐标。4.3.47200bit/s的信号码元编码经扰码待发送的数据流,按3个连续数据比特分为一一组,这些数据比特照其出现的时间排序。如图1所示,每组前两个比特Q1和Q2,(这里n表示该组的序号),按照表1规定首先差分编码为Y1,和Y2。

两个差分编码比特Y1,和Y2输入到系统卷积编码器生成一余比特YO,该穴余比特和3个载有信息的比特Y1n、Y2和Q3按图5所示的信号空间状态图映射成为发送的信号码元坐标。90

010100

110101

011011

000100

111101

010110

010011

010001

110000

100111

100010

000001

111000

110111

110010

111110

111011

001100

101101

001110

001011

100100

011101

000111

Q0Q010

001001

101000

101111

101010

100001

011000

011100

190101

101110

101011

101100

001101

000110

000011

011001

100000

001111

001010

101001

001000

111111

111010

注:二进制数指Q5,、Q4、Q3,、Y2、Y1、Y0元。A,B、C和D指的是同步信号码元。110110

110011

111100

000101

100110

100011

110100

010101

图312000bit/s数据信号速率下格状编码所使用的64点信号结构o101H

010010

111001

000000

011111

011010

110001

010000

YD/T853—1996

注:二进制数指Q4aQ3折、Y2、Y1,、YOm。A、B、C和D指的是同步信号码元。0

图49600bit/s数据信号速率下格状编码所使用的32点信号结构90°

注:二进制数指Q3、Y2、Y1、YOn。A、B、C和D指的是同步信号码元,05

图57200bit/s数据信号速率下格状编码所使用的16点信号结构4.4发送频谱

当扰码器输入为连续的二进制1时,相对600Hz到3000Hz之间的最大功率密度,在600Hz和3000Hz点应衰减4.5dB±2.5dB。532

5接口电路

接口电路览表

YD/T853—1996

本建议中参照V.24的接口电路编号,只是在功能上与这些电路等效,并非指物理上实现这些电路,例如参考电路103应理解为在功能上相当于电路103(见表2)表2接口电路

108/1或

信号地或公用回线

发送数据

接收数据

请求发送

准备发送

数据设备准备好

把数据设备接至线路(注)

数据终端准备好(注)

数据信道接收线路信号检测器

发送机信号码元定时(源于DCE)接收机信号码元定时(源于DCE)呼指示器

注:这条电路能做为电路108/1或电路108/2运行。5.2发送数据

在电路103上,调制解调器将接收来自传真控制功能单元的数据:在电路103上的数据处于电路114的控制之下。

5.3接收数据

在电路104_上,调制解调器将数据传送到传真控制功能单元;在电路104上的数据处于电路115的控制之下。

5.4定时配置

在调制解调器中应包括时钟,以提供具有电路114发送机信号码元定时和电路115接收机信号码元定时的传真控制功能。

5.5数据速率控制

数据速率控制将由调制解调器和传真机控制功能之间的连接来提供;该连接特性超出了本标准研究的范围。

5.6电路106和109的响应时间

在第7章中规定的训练和同步序列之后,紧接着应在3.5ms以内,电路106应从断(OFF)状态转变到通(ON)状态或电路105应从通转变为断的状态。电路109从断转变为通的状态。是第7章中规定的训练序列的一部分。在调制解调器的线路终端出现接收电平下降到5.7中规定的相关门限以下后的30ms到50ms时间内,电路109应回到断状态。在初始握手之后,当调制解调器线路终端的接收电平超过5.7规定的相关门限后的40到205ms时间内,电路109应转为通状态。5.7电路109门限

≥-43 dBm 通

<-48 dBm 断

YD/T 853--- 1996

电平在-43dBm和一48dBm之间电路109的状态未作规定,信号检测器呈现滞后作用,这样从断到通时的电平至少应比从通到断转换的电平大2dB。接收经扰码的二进制1时,在调制解调器的输入端规定电路109的门限,在已知传输条件的地方,允许主管部门改变这些门限。注:电路109通到断的响应时间应在规定的限值内适当选择,以确保所有有效的数据比特已出现在电路104上。5.8籍位

在执行位的场合,当电路105在通状态时,DCE应使电路104保持在二进制“1\状态及电路109保持在断状态,而且在要求对电路104进行保护以防虚假信号影响的场合,随着电路105从通到断的转变,DCE还要保持上述状态150±25ms。按照系统的考虑附加延时的使用是任选的。6扰码器和解扰器

在调制解调器中应装有具有下列生成多项式的自同步扰码器和解扰器:1 → X-18 +X~23

在发送端,扰码器应当用生成多项式除以信息数据序列。这除得商的系数,按降幂取值形成扰码器输出端数据序列。在接收端,解码器用生成多项式乘以接收到的数据序列,以恢复信息序列。7操作序列

7.1训练和同步序列

在表3规定了训练信号和同步信号序列。长训练序列用于初始建立连接或在需要重新训练时使用。再同步序列用于成功的长训练之后的再同步。表3训练和同步信号

第1段

ABAB交替

长训练

再同步

第2段

均衡器训练信号

7.1.1第1段:ABAB交替

第3段

桥接信号

此段由交替的A和B状态组成,如图2到5所示。7.1.2第2段:均衡器训练信号

第4段

经扰码的1

总符号间隔

此段由如图2到图5所示的四个信号码元A、B、C和D的顺序传送组成大约时间(ms)

均衡器调节码型通用多项式1+X-18+X-23数据扰码器生成4800bit/s速率的伪随机序列。在第2阶段期间,任何差分正交编码均无效,并且如表4所示对经扰码的双比特进行编码。随着二进制1加到输入,应选择初始扰码器状态,以产生下列扰码器输出码型和相应的信号码元:四相训练信号的编码

7.1.3第3段桥接信号

YD/T 853 ---1996

第2段

双比特

信号状态

仅在初始长训练期闻使用这段,由发送8次的16bit二进制序列组成。按表5规定的序列进行扰码,并按照图2到图5规定的信号码元A、B、C和D以4800bit/s速率进行传送。表5

第3段比特指明

正如BO比特输入扰码器中一样,它是数据流中的第一·比特。9

2比特4-6,810,1214的任何一种使用有待进一步研究。某些现有设备可能将这些比特中的1个或多个置为二进制1:应忽略这些比特。按照表6的规定将双比特进行差分编码。B

应该用前一段的最后一个比特来启动差分编码器。头二个比特和随后每16比特序列的双比特应当作为一个信号状态来进行编码。表6第3段双比特编码

双比特

7.1.4第4段

相位变化

+90度

180度

应以信道数据比特速率发送经扰码的二进制1。对长训练序列,应使用第3段的第一比特来启动差分编码器。对短训练序列,使用第二段的最后…一个比特来启动差分编码器应将卷积编码器初始状态置为0。前输出/输出

A/B,B/C,C/D),D/A

A/A,B/B.C/C.D/D

A/C.B/D.C/A,D/B

A/D,B/A,C/B,D/C

扰码器应以比特速率进行计时,扰码器输出序列按照第六章中的规定进行编码。该初始扰码器的状态由前一段最后一个符号的间隔而产生。第4段持续时间是48个符号间隔。在第4段结束时电路106转为通(ON).并将数据加到数据扰码器的输入端。

在接收第4段期间将电路109转变为ON。7.2关断序列

在电路105由通转变到断时,其余的数据或在已传送重新训练规程期间训练检测信号之后发送的线路信号如表7所示。

连续经扰码的1

SI表示符号间隔,

YD/T853—1996

表 7关断序列

各段总和

不发送能量

大致时间

注:如果出现断序列期间发生电路105从断到通的转变,不考虑这个状态,直到出现断序列结束为止。7.3讲话者回声防止(TEP)信号

在传送训练和同步序列之前可任选发送TEP信号。该TEP信号应由时长为185ms到200ms的未调制载频后随20ms到25ms静默时间组成。当使用时,该TEP信号应作为训练序列的一部分予以考虑。用于获得TEP信号期望效益的另一种方法有待进一步研究。536

本标准等效采用国际电报电话咨询委员会(CCITT)建议V.17(1991年版本)。用于检测速率高达14400bit/s传真用二线调制解调器本标准由邮电部电信科学研究规划院提出并归口。本标准起草单位:邮电部电信传输研究所。本标准主要起草人:苟雅莉、王新京、崔进水。525

YD/T853-1996

CCITT前言

CCITT(国际电报电话咨询委员会)是国际电信联盟(ITU)的常设机构。CCITT负责技术、操作资费问题的研究,并且为了实现全世界电信标准化,对上述问题发布建议。每四年举行一次的CCITT全体会议确定研究课题,并批准所属研究组提交的建议。在两次全体会议期间CCITT成员对建议的审议是以CCITT2号决议(墨尔本1988)的程序进行的。建议V.17由第17研究组制定,并在1991年2月22日以2号决议的程序被批准。CCITT注

在本建议中,“主管部门”词是指电信主管部门和经认可的私营机构二者的简称526

1范围

中华人民共和国通信行业标准

速率高达14400bit/s传真用

二线调制解调器的技术要求

YD/T853.1996

eqv CCITT V: 17 : 1991

本标准规定速率高达14400bit/s(简称高速)文件传真机用的调制解调器的调制方法和操作程序。本标准适用于高速文件传真机的研究、开发和生产,为高速文件传真机的互通提供技术依据。2引用标准

下列标准所包含的条文,通过在本标准中引用而构成为本标准的条文。本标准出版时,所示版本均为有效。所有标准都会被修订,使用本标准的各方应探讨,使用下列标准最新版本的可能性。CCITTV.24:1988数据终端设备(DTE)和数据电路终接设备(DCE)之间的接口电路定义表3引言

本建议规定了高速传真机应用的调制解调器的调制方法和操作程序。对于传真机传输应用的操作方法和其他特性应参考适当的T系列建议,因为一般传真三类机应用的高速调制解调器的有关建议与本标准有区别。调制解调器的基本特性如下:

a)提供下列数据信号速率下的半双工操作:-14400bit/s同步;

-—12000 bit/s同步;

9600bit/s同步;

-7200bit/s同步。

b)在2400 Bd(波特)下以同步线路传输的正交调幅。c)包括数据扰码器、自适应均衡器和八状态格状编码。d)用于训练和同步的二序列:长训练和再同步。4线路信号

4.1载波频率

信道载波频率是1800Hz士1Hz。接收机在收到载波频率最大偏移为±7Hz的信号时应能工作。4.2调制

调制速率为2400±0.01%Bd。

4.3信号码元编码

4.3.114400bit/s的信号码元编码经扰码待发送的数据流按6个连续数据比特分为一组,这些数据比特按照其出现的时间排序。如图1所示,每组的前两个比特Q1和Q2(这单n表示该组的序号),按照表1的规定首先差分编码为Y1和Y2元。

中华人民共和国邮电部1996-05-08批准1996-11-01实施

YD/T853—1996

两个差分编码比特Y1.和Y2,输入到系统卷积编码器生成一个亢余比特YO元。该穴余比特和6个载有信息的比特Y1,Y2折,Q3mQ4元、Q5,和Q6%按图2所示的信号空间状态映射成为发送的信号码元坐标。

表1格状编码使用的差分编码

Y1, Y2,

前一输入

见表1

差分编码器

YD/T853---1996

卷积编码器

图114400、12000、9600、7200bit/s信号速率的格状编码器信号码元

见图2

到图5

YD/T 853--1996

0000110

0000011

1100100

1011101

1010110www.bzxz.net

1010011

1000100

0001101

1001111

1001010

1100001

1011000

1101111

1101010

1000001

0001000

0001110

0001011

1110100

1111101

0010110

0010011

0100100

0011101

1110110

-811100m

1001100

0000101

1000111

1000010

1110001

1111000

0101111

0101010

0100001

0011000

1010100

1101101

0011110

0011011

0110100

0111101

0110110

—40110011

-6 1111111

1111010

1001001

0000000

0101100

0010101

1100110

1100011

1010001

1101000

0100111

0100010

0110001

0111000

-2 0111111

0111010

0101001

0010000

1011111

1011010

1011110

1011011

0010100

0101101

0111110

0111011

0111100

0110101

0100110

0100011

1101100

1010101

H00111

1100010

0010001

0101000

0110111

0110010

0111001

0110000

0011111

0011010

1101001

1010000

0000100

1001101

1111011

0011100

0100101

0101110

0101011

1111100

1110101

1000110

1000011

0000001

1001000

1110111

1110010

0011001

0100000

0010111

0010010

0001100

1000101

1101110

1101011

1011100

il11001?

1100101

1110000

0001111

0001010

1001110

1001011

0001001

1000000

1010111

1010010

1011001

1100000

Q000111

0000010

注:二进制数指Q6m、Q5、Q4,、Q3、Y2、Y1n、YOn。A、B.C和D指的是同步信号码元。图214400bit/s数据信号速率下格状编码所使用的128点信号结构4.3.212000bit/s的信号码元编码经扰码待发送的数据流,按5个连续数据比特分为一组,这些数据比特照其出现的时间排序。如图1所示,每组前两个比特Q1,和Q2(这里n表示该组的序号),按照表1规定首先差分编码为Y1,和Y2.

两个差分编码比特Y1,和Y2,输入到系统卷积编码器生成一亢余比特YOn。该穴余比特和5个载有信息的比特Y1、Y2折Q3n、Q4m和Q5按图3所示的信号空间状态图映射成为发送的信号码元坐标。4.3.39600bit/s的信号码元编码经扰码待发送的数据流,按4个连续数据比特分为一组,这些数据比特照其出现的时间排序。如图1所示,每组前两个比特Q1,和Q2,(这里n表示该组的序号),按照表1规定首先差分编码为Y1.和Y2元

两个差分编码比特Y1.和Y2输入到系统卷积编码器生成一亢余比特YO。该余比特和4个载530

YD/T853--1996

有信息的比特Y1,、Y2mQ3,和Q4,按图4所示的信号空间状态图映射成为发送的信号码元坐标。4.3.47200bit/s的信号码元编码经扰码待发送的数据流,按3个连续数据比特分为一一组,这些数据比特照其出现的时间排序。如图1所示,每组前两个比特Q1和Q2,(这里n表示该组的序号),按照表1规定首先差分编码为Y1,和Y2。

两个差分编码比特Y1,和Y2输入到系统卷积编码器生成一余比特YO,该穴余比特和3个载有信息的比特Y1n、Y2和Q3按图5所示的信号空间状态图映射成为发送的信号码元坐标。90

010100

110101

011011

000100

111101

010110

010011

010001

110000

100111

100010

000001

111000

110111

110010

111110

111011

001100

101101

001110

001011

100100

011101

000111

Q0Q010

001001

101000

101111

101010

100001

011000

011100

190101

101110

101011

101100

001101

000110

000011

011001

100000

001111

001010

101001

001000

111111

111010

注:二进制数指Q5,、Q4、Q3,、Y2、Y1、Y0元。A,B、C和D指的是同步信号码元。110110

110011

111100

000101

100110

100011

110100

010101

图312000bit/s数据信号速率下格状编码所使用的64点信号结构o101H

010010

111001

000000

011111

011010

110001

010000

YD/T853—1996

注:二进制数指Q4aQ3折、Y2、Y1,、YOm。A、B、C和D指的是同步信号码元。0

图49600bit/s数据信号速率下格状编码所使用的32点信号结构90°

注:二进制数指Q3、Y2、Y1、YOn。A、B、C和D指的是同步信号码元,05

图57200bit/s数据信号速率下格状编码所使用的16点信号结构4.4发送频谱

当扰码器输入为连续的二进制1时,相对600Hz到3000Hz之间的最大功率密度,在600Hz和3000Hz点应衰减4.5dB±2.5dB。532

5接口电路

接口电路览表

YD/T853—1996

本建议中参照V.24的接口电路编号,只是在功能上与这些电路等效,并非指物理上实现这些电路,例如参考电路103应理解为在功能上相当于电路103(见表2)表2接口电路

108/1或

信号地或公用回线

发送数据

接收数据

请求发送

准备发送

数据设备准备好

把数据设备接至线路(注)

数据终端准备好(注)

数据信道接收线路信号检测器

发送机信号码元定时(源于DCE)接收机信号码元定时(源于DCE)呼指示器

注:这条电路能做为电路108/1或电路108/2运行。5.2发送数据

在电路103上,调制解调器将接收来自传真控制功能单元的数据:在电路103上的数据处于电路114的控制之下。

5.3接收数据

在电路104_上,调制解调器将数据传送到传真控制功能单元;在电路104上的数据处于电路115的控制之下。

5.4定时配置

在调制解调器中应包括时钟,以提供具有电路114发送机信号码元定时和电路115接收机信号码元定时的传真控制功能。

5.5数据速率控制

数据速率控制将由调制解调器和传真机控制功能之间的连接来提供;该连接特性超出了本标准研究的范围。

5.6电路106和109的响应时间

在第7章中规定的训练和同步序列之后,紧接着应在3.5ms以内,电路106应从断(OFF)状态转变到通(ON)状态或电路105应从通转变为断的状态。电路109从断转变为通的状态。是第7章中规定的训练序列的一部分。在调制解调器的线路终端出现接收电平下降到5.7中规定的相关门限以下后的30ms到50ms时间内,电路109应回到断状态。在初始握手之后,当调制解调器线路终端的接收电平超过5.7规定的相关门限后的40到205ms时间内,电路109应转为通状态。5.7电路109门限

≥-43 dBm 通

<-48 dBm 断

YD/T 853--- 1996

电平在-43dBm和一48dBm之间电路109的状态未作规定,信号检测器呈现滞后作用,这样从断到通时的电平至少应比从通到断转换的电平大2dB。接收经扰码的二进制1时,在调制解调器的输入端规定电路109的门限,在已知传输条件的地方,允许主管部门改变这些门限。注:电路109通到断的响应时间应在规定的限值内适当选择,以确保所有有效的数据比特已出现在电路104上。5.8籍位

在执行位的场合,当电路105在通状态时,DCE应使电路104保持在二进制“1\状态及电路109保持在断状态,而且在要求对电路104进行保护以防虚假信号影响的场合,随着电路105从通到断的转变,DCE还要保持上述状态150±25ms。按照系统的考虑附加延时的使用是任选的。6扰码器和解扰器

在调制解调器中应装有具有下列生成多项式的自同步扰码器和解扰器:1 → X-18 +X~23

在发送端,扰码器应当用生成多项式除以信息数据序列。这除得商的系数,按降幂取值形成扰码器输出端数据序列。在接收端,解码器用生成多项式乘以接收到的数据序列,以恢复信息序列。7操作序列

7.1训练和同步序列

在表3规定了训练信号和同步信号序列。长训练序列用于初始建立连接或在需要重新训练时使用。再同步序列用于成功的长训练之后的再同步。表3训练和同步信号

第1段

ABAB交替

长训练

再同步

第2段

均衡器训练信号

7.1.1第1段:ABAB交替

第3段

桥接信号

此段由交替的A和B状态组成,如图2到5所示。7.1.2第2段:均衡器训练信号

第4段

经扰码的1

总符号间隔

此段由如图2到图5所示的四个信号码元A、B、C和D的顺序传送组成大约时间(ms)

均衡器调节码型通用多项式1+X-18+X-23数据扰码器生成4800bit/s速率的伪随机序列。在第2阶段期间,任何差分正交编码均无效,并且如表4所示对经扰码的双比特进行编码。随着二进制1加到输入,应选择初始扰码器状态,以产生下列扰码器输出码型和相应的信号码元:四相训练信号的编码

7.1.3第3段桥接信号

YD/T 853 ---1996

第2段

双比特

信号状态

仅在初始长训练期闻使用这段,由发送8次的16bit二进制序列组成。按表5规定的序列进行扰码,并按照图2到图5规定的信号码元A、B、C和D以4800bit/s速率进行传送。表5

第3段比特指明

正如BO比特输入扰码器中一样,它是数据流中的第一·比特。9

2比特4-6,810,1214的任何一种使用有待进一步研究。某些现有设备可能将这些比特中的1个或多个置为二进制1:应忽略这些比特。按照表6的规定将双比特进行差分编码。B

应该用前一段的最后一个比特来启动差分编码器。头二个比特和随后每16比特序列的双比特应当作为一个信号状态来进行编码。表6第3段双比特编码

双比特

7.1.4第4段

相位变化

+90度

180度

应以信道数据比特速率发送经扰码的二进制1。对长训练序列,应使用第3段的第一比特来启动差分编码器。对短训练序列,使用第二段的最后…一个比特来启动差分编码器应将卷积编码器初始状态置为0。前输出/输出

A/B,B/C,C/D),D/A

A/A,B/B.C/C.D/D

A/C.B/D.C/A,D/B

A/D,B/A,C/B,D/C

扰码器应以比特速率进行计时,扰码器输出序列按照第六章中的规定进行编码。该初始扰码器的状态由前一段最后一个符号的间隔而产生。第4段持续时间是48个符号间隔。在第4段结束时电路106转为通(ON).并将数据加到数据扰码器的输入端。

在接收第4段期间将电路109转变为ON。7.2关断序列

在电路105由通转变到断时,其余的数据或在已传送重新训练规程期间训练检测信号之后发送的线路信号如表7所示。

连续经扰码的1

SI表示符号间隔,

YD/T853—1996

表 7关断序列

各段总和

不发送能量

大致时间

注:如果出现断序列期间发生电路105从断到通的转变,不考虑这个状态,直到出现断序列结束为止。7.3讲话者回声防止(TEP)信号

在传送训练和同步序列之前可任选发送TEP信号。该TEP信号应由时长为185ms到200ms的未调制载频后随20ms到25ms静默时间组成。当使用时,该TEP信号应作为训练序列的一部分予以考虑。用于获得TEP信号期望效益的另一种方法有待进一步研究。536

小提示:此标准内容仅展示完整标准里的部分截取内容,若需要完整标准请到上方自行免费下载完整标准文档。

标准图片预览:

- 其它标准

- 热门标准

- 通信行业标准(YD)

- YD/T1966-2009 移动通信用 50Ω 射频同轴跳线

- YD/T5178-2017 通信管道人孔和手孔图集

- YD/T2318-2011 通信基站用新风空调一体机技术要求和试验方法

- YD/T1480-2006 基于软交换的应用服务器测试方法

- YD/T2781-2014 电信和互联网服务用户个人信息保护定义及分类

- YD/T1423-2005 800MHz CDMA 数字蜂窝移动通信网定位业务: L1 接口技术要求

- YD/T2769-2014 通信户外机房用温控设备 第2部分相变材料温控设备

- YD/T1769-2008 光线路保护管理系统技术要求

- YD/T2880-2015 域名服务业务连续性管理要求

- YD/T2761-2014 通信电源用交联聚烯烃绝缘电缆

- YD/T2780-2014 VHF/UHF 无线电管制系统开场测试参数和测试方法

- YD/T1000-1999 提供国际帧中继 SVC 业务的数据网的性能

- YD/T1187-2006 ADSL/VDSL分离器技术要求及测试方法

- YD/T1846.2-2009 2GHz TD-SCDMA 数字蜂窝移动通信网高速上行分组接入(HSUPA) Uu 接口层2技术要求 第2部分: RLC 协议

- YD/T2583.3-2016 蜂窝式移动通信设备电磁兼容性能要求和测量方法 第3部分:多模基站及其辅助设备

- 行业新闻

请牢记:“bzxz.net”即是“标准下载”四个汉字汉语拼音首字母与国际顶级域名“.net”的组合。 ©2025 标准下载网 www.bzxz.net 本站邮件:wymp4wang@gmail.com