- 您的位置:

- 标准下载网 >>

- 标准分类 >>

- 电子行业标准(SJ) >>

- SJ 2559-1984 S-100总线规范

标准号:

SJ 2559-1984

标准名称:

S-100总线规范

标准类别:

电子行业标准(SJ)

标准状态:

现行-

发布日期:

1984-12-25 -

实施日期:

1985-10-01 出版语种:

简体中文下载格式:

.rar.pdf下载大小:

2.16 MB

手机扫码下载更方便

点击下载

标准简介:

标准下载解压密码:www.bzxz.net

本标准适用于通过S-100总线进行互连的计算机系统部件的接口系统。凡具备下列条件的激处理器计算机系统或系统中的若干部分,均在本标准适用范围之内。 SJ 2559-1984 S-100总线规范 SJ2559-1984

部分标准内容:

中华人民共和国电子工业部部标准SJ2559-84

S-100总线规范

1984-12-25发布

中华人民共和国电子工业部

1985-10-01实施

1总述

1.1范围

中华人民共和国电子工业部部标准S-100总线规范

本标准适用于通过S一100总线进行互连的计算机系统部件的接口系统。SJ2559-84

凡具备下列条件的微处理器计算机系统或系统中的若干部分,均在本标准适用范围之内。

a,互连设备之间交换的数据为数字量。b,互连设备的总数最多为22个。c.互连设备之间的传输路径总长度小于或等于63.5cm(25in)。d.总线上任何信号的最大转换速率小于等于6MHz。1.2目的

本标准育在:

a.为新计算机系统部件的设计人员定义一种合理的、通用的接口系统,从而保证S-100总线计算机系统无论在目前还是将来都能够兼容。b,为微处理器计算机系统的用户提供兼容的设备系列,这些设备无须改动便可以明确无误的方式进行通信,并可构成以模块方式扩充的计算机系统。c,使不同厂家生产的设备可互连成一个系统。d.规定与本总线系统有关的术语和定义。e.定义一种系统,该系统对与之相连接的设备的性能特性限制最少。f.定义一种价格相对较低的系统,并允许廉价设备互连。g.定义种容易使用的系统。

1.3定义

下列定义仅用于本标准。本条只给出一般定义,详细定义在其它相应条款中给出。1.3.1一般系统术语

1.3.1.1兼容性(compatibility):按本标准2、3、4章进行设计时,设备无修改即可互连和使用的程度。

1.3.1.2设备(device):在一块或多块插件板上的一个电路或多个电路的逻辑组合,它们通过总线可以与其它符合本定义的设备相互作用。1.3.1.3接口(interface):计算机系统各部分之间共享的电气界面。信息通过它进行传输。

电子工业部1984-12-02发布

1985-10-01实施

SJ2559-84

1.3.1.4接口系统(interfacesystem):在-组设备间实现明确无误的通信所必须的、独立于设备的功能、电气和机械接口要素。典型的接口系统要素有:驱动器与接收器电路、信号线描述、时序与控制规约、数据传输协议和功能逻辑电路等。1.3.1.5K字节(kilobyte):1024=2101.3.1.6M字节(megabyte):1048576=221.3.1.7系统(system):一套相互关联的部件,它迹过执行规定的功能来实现给定的目的。

1.3.2信号与通路

1.3.2.1有效(active):信号处于逻辑值为“真”的状态。1.3.2.2激励(activate):同“建立”(assert)。1.3.2.3建立(assert):使信号线从逻辑“伪”(无效)状态转变成逻辑“真(有效)状态。“真”取有效状态可以是高态也可以是低态,每一信号均有具体规定。1.3.2.4双向总线(bidirectionalbus):为单个设备或套设备使用的、具有输入和输出两种数据传输方式的总线。1.3.2.5位并行(bit-parallel):用来载递信息的、同时存在于同样数量信号线上的一组数据位。这些位并行数据位可一起用作一个整体,也可以用作独立的数据位。

1.3.2.6总线(bus):接口系统所使用的一组信号线。设备通过它相互连接和传递信息。

1.3.2.7总线周期(buscycle):实现总线数据传输所需的电脉冲基本序列。一个总线周期必须包括至少三个总线状态。1.3.2.8总线状态(busstate):一个总线状态的持续时间为一个时钟周期。它的开始和结束恰好处于系统时钟中的上升沿之前。每一个总线周期中必须至少有三个总线状态。

1.3.2.9字节(byte):组作为整体看待的,对应于二进制数字的位并行信号,它由八个二进制位构成。其最高有效位脚标为7,最低有效位脚标为0。1.3.2.10字节串(byte-serial):经公共总线载递信息的位并行数据字节序列。

1.3.2.11撤消(deactivate):使信号由逻辑“真”(有效)状态转变成逻辑“伪”(无效)状态,它是“建立”的逆操作。1.3.2.12高态(highstate):用来建立某种特定消息内容的较高的正信号电平。这一特定消息内容仅由两个二进制逻辑状态之一表征。1.3.2.13无效(inactive):信号处于逻辑伪”状态。1.3.2.14低态(1owstate):用来表征某种特定消息的较低的正信号电平,这一特定消息仅由两个二进制逻辑状态之一表征。2

SJ2559-84

1),数据从一点传递到另一点的物理表示。在本标准范围1.3.2.15信号(signal

内,信号仅指数字电信号。

1.3.2.16信号电平(signallevel):相对于任一选定的参考量(本标准中为电压)的信号量值。

1.3.2.17信号线(signalline):接口系统中用来在互连设备之间传送消息的组信号导体之。

1.3.2.18信号参数(signalparameter):一种电量参数,其值或值的序列用来传递信息。

1.3.2.19单向总线(unidirectionalbus):设备用来单向传送消息的总线,它或者只能输出或者只能输入。

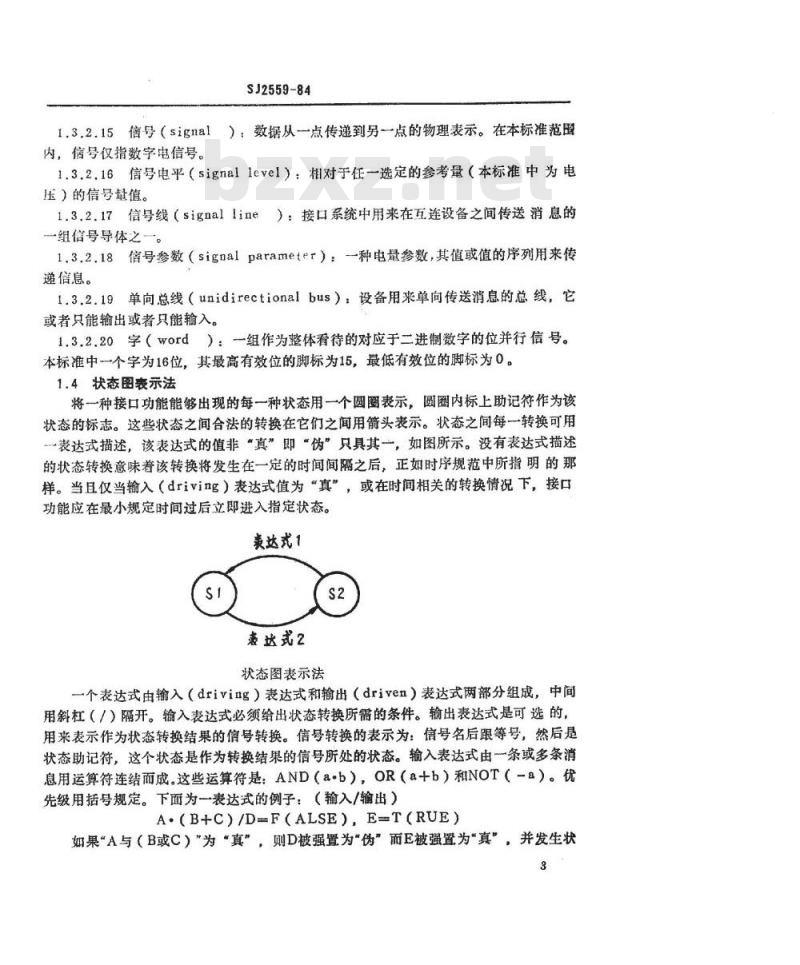

1.3.2.20字(word):一组作为整体看待的对应于二进制数字的位并行信号。本标准中一个字为16位,其最高有效位的脚标为15,最低有效位的脚标为0。1.4状态图表示法

将一种接口功能能够出现的每一种状态用一个圆圈表示,圆圈内标上助记符作为该状态的标志。这些状态之间合法的转换在它们之间用箭头表示。状态之间每一转换可用~表达式描述,该表达式的值非“真”即“伪”只具其一,如图所示。没有表达式描述的状态转换意味着该转换将发生在一定的时间间隔之后,正如时序规范中所指明的那样。当且仅当输入(driving)表达式值为“真”,或在时间相关的转换情况下,接口功能应在最小规定时间过后立即进入指定状态。爽达式1

表达式2

状态图表示法

一个表达式由输入(driving)表达式和输出(driven)表达式两部分组成,中间用斜杠(/)隔开。输入表达式必须给出状态转换所需的条件。输出表达式是可选的,用来表示作为状态转换结果的信号转换。信号转换的表示为:信号名后跟等号,然后是状态助记符,这个状态是作为转换结果的信号所处的状态。输入表达式由一条或多条消息用运算符连结而成。这些运算符是:AND(a·b),OR(a+b)和NOT(a)。优先级用括号规定。下面为一表达式的例子:(输入/输出)A·(B+C)/D=F(ALSE),E=T(RUE)如果“A与(B或C)”为“真”,则D被强置为\伪”而E被强置为“真”,并发生状3

态转换。

SJ2559-84

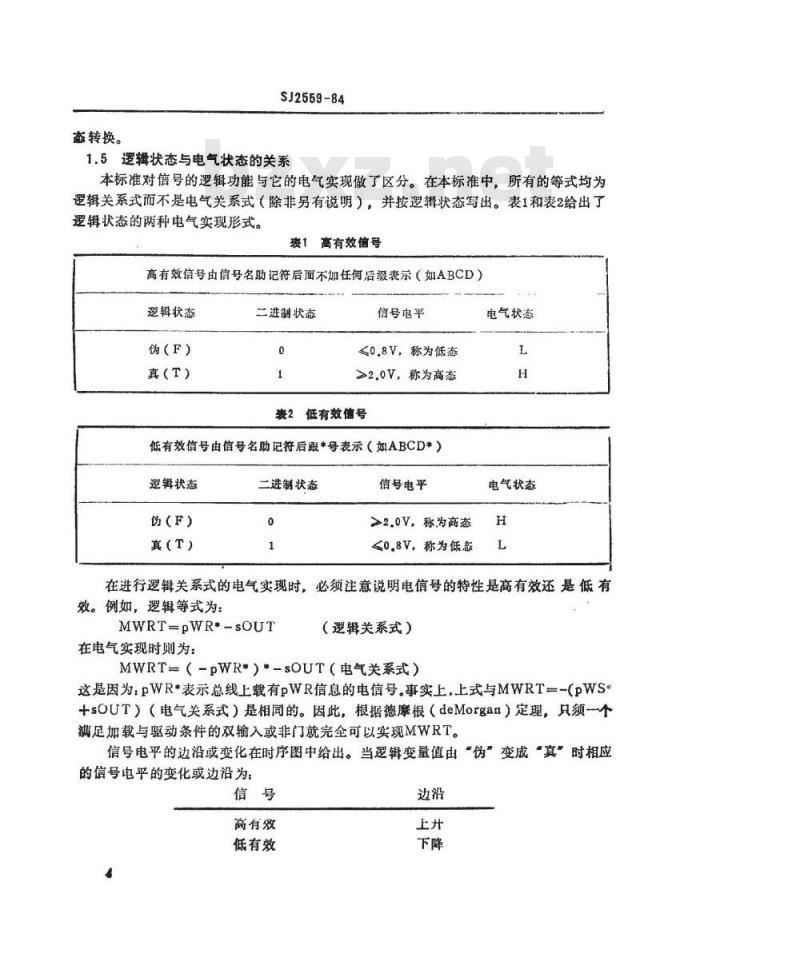

1.5逻辑状态与电气状态的关系

本标准对信号的逻辑功能与它的电气实现做了区分。在本标准中,所有的等式均为逻辑关系式而不是电气关系式(除非另有说明),并按逻辑状态写出。表1和表2给出了逻辑状态的两种电气实现形式。表1

高有效信号

高有效信号由信号名助记符后面不加任何后级表示(如ABCD)逻辑状态

伪(F)

真(T)

二进制状态

信号电平

≤08V,称为低态

>2.0V,称为高态

表2低有效信号

低有效信号由信号名助记符后跟*号表示(如ABCD*)逻辑状态

伤(F)

真(T)

二进制状态

信号电平

>2.0V,称为高态

<0.8V,称为低态

电气状态

电气状态

在进行逻辑关系式的电气实现时,必须注意说明电信号的特性是高有效还是低有效。例如,逻辑等式为:

MWRT=pWR*-sOUT

在电气实现时则为:

(逻辑关系式)

MWRT=(-pWR*)*-sOUT(电气关系式)这是因为:pWR*表示总线上载有pWR信息的电信号.事实上,上式与MWRT=-(pWS+sOUT)(电气关系式)是相同的。因此,根据德摩根(deMorgan)定理,只须一个满足加载与驱动条件的双输入或非门就完全可以实现MWRT。信号电平的边沿或变化在时序图中给出。当逻辑变量值由“伪”变成“真”时相应的信号电平的变化或边沿为:

高有效

低有效

SJ2559-84

状态图中的状态关系式均按逻辑状态给出而不用电气状态。作为后缀的星号*并不是否定运算符,它只是一个与信号名相连的标志符(如同一个注释或脚注),用来表示逻辑状态与电气状态之间的关系。就是说,当信号线呈现低电平时该变量是“真”值。前缀负号“”为逻辑否定运算符,它与上横线的意义相同。为清楚起见,在必要时可用括号标出否定的范围。

1.6接口系统概述

1.6.1接口系统的目的

接口系统总的目的是提供一种高效率的通信链路,通过它,消息能以明晰准确的方式在一组互连设备之间传递。

接口系统中的消息划分为两大类a.用于控制接口系统本身的消息,称作接口消息。b,经接口系统传递且为该系统互连的设备所使用,但又不是接口系统本身的一部份,这种消息称作设备相关消息(如数据)。本标准所描述的接口系统仅包括接口消息的功能与电气规范,对于设备相关消息的特性和意义本标准不作规定。

1.6.2基本通信能力

一个高效率的通信链路须具有两种基本的功能部件,才能对设备之间的信息流实施组织和管理:

a,起总线主设备作用的设备。

b.起总线从设备作用的设备。

总线主设备和总线从设备之间所有的信息传输均由统一化的总线周期实现。该总线周期由总线主设备产生,为被寻址的总线从设备所响应。在本标准所描述的接口系统中,8.总线主设备能够产生完成一个总线周期所必须的全部接口消息,并借此访问全部或部分总线从设备。该主设备可以从被访问的从设备接收或向被访问的从设备发送设备相关消息作为总线周期的一部分。b,总线从设备监视全部总线周期。因此,它能被总线主设备访问并向主设备发送或接收主设备发出的设备相关信息。总线主设备和总线从设备功能既可单独地也可共同地存在于由本标准定义的接口系统所互连的插件板上。

1.6.3消息通路与总线结构

S100总线接口系统由一组信号线构成,这组信号线用来传递互连设备间的全部信息一一接口消息和设备相关消息。S一100总线的结构归结为八组信号线和一组电源线,如表3所示。5

2功能规范

(1)数据总线

(2)地址总线

(3)状态总线

(4)控制输出总线

(5)控制输入总线

(6)TMA控制总线

(7)向量中断总线

SJ2559-84

表3总线结构

(8)其它各种用途总线

(9)电源总线

2.1功能划分

16条信号线

16条或24条信号线

8条信号线

5条信号线

6条信号线

8条信号线

8条信号线

16条信号线

9条电源线

由接口系统互连的设备按产生还是接收接口信息分为两类一一总线主设备和总线从设备。

起总线主设备作用的设备负责形成总线周期并产生为执行正确的总线周期所需的全部信号。这些信号称作M类信号,它们由地址、状态和控制总线信号组成。设备相关消息从数据总线发送和接收。

总线主设备又分为两类:一类为永久性主设备,另一类是暂时性主设备。水久性总线主设备(通常为CPU)是接口系统中具有最高优先级的主设备。暂时性主设备可向永久性主设备请求占用总线任意数量的总线周期,然后将总线控制权交还给永久性总线主设备。总线控制权由永久性主设备交给暂时性主设备然后又返回永久性主设备这一转移过程称为TMA(TemporrymasterAccess)周期。永久性总线主设备和暂时性总线主设备的区别如下:8.接口系统中只能有-个永久性主设备存在,面一个系统中同时存在的暂时性主设备最多可达十六个。

b.暂时性主设备不提供TMA周期,就是说,没有嵌套的TMA操作。起总线从设备作用的设备是总线周期接收者。总线从设备监视所有的总线周期,且在某个特定总线周期中被寻址,便从数据线发送或接收所要求的设备相关消息。总线主设备必须产生规定的一组信号来形成一个正确的总线周期,而总线从设备只需检查和产生那些与总线主设备通信所必须的总线信号子集。2.2信号线

2.2.1概述

对现行总线主设备来说总线是消息通路的集合。它们是:a.地址总线:

b.状态总线:

c.数据输入/输出总线

d.控制输出总线:

e.控制输入总线:

f.TMA控制总线:

g.向量中断总线:

h.其它各种用途总线。

SJ2559-84

每一总线的特性和用途在以下各款中规定。除另有说明外,所有总线信号线均为三态线。

2.2.2地址总线

地址总线由16或24条位并行信号线组成,为现行总线周期中的通信提供具体的存储单元或输入/输出设备的地址。

所有的总线主设备必须建立A0至A15地址位,而A16至A23则可根据需要作为扩充使用。

地址总线的有效性在2.了.2中定义。地址线全部为三态线。

表4概括了各种总线周期所使用的地址。表4不同总线周期的地址使用

周期类型

存储器读

存储器写

M1(取指周期)

中断响应

暂停响应

标推编址

A15~A0

A7~A0

注:输入输出的标准编址见2.2.2.4。2.2.2.1标准存储器编址

扩展编址

A23~A0

A15~A0

标准存储器地址总线由16条线构成,寻址能力达64K字节存储单元。这16条线顺序记为A15~A0,A15为最高有效位。2.2.2.2扩展存储器编址

扩展的存储器地址总线由24条线组成,可对16M字节的存储单元进行导址。这24条线记为A23~A0,其中A23为最高有效位。7

2.2.2.3PHANTOM*

SJ2559-84

PHANTOM*信号提供了以一个公共地址单元覆盖两个存储器从设备的能力。当PHANTOM*信号线被激励时,影象(Phantom)存储器从设备有效而常规(norm-al)存储器无效。在PHANTOM*信号建立时,所有的常规存储器从设备必须能被禁止。在读和写周期出现PHANTOM*信号时也必须将常规存储器禁止。2.2.2.4标准输入/输出设备编址标准I/O设备地址总线有8条线,A7~A0,可对256个I/O设备编址。A7为最高有效位。

注:I/O设备地址习惯上总放在高序地址字节A15~A8.鼠然这一增尴是可以接受的,但是并不推荐在新的设计中采用,因为它使扩膳的I/O设备编址复杂化了。标准I/O从设备决不应只做靠对高序地证学节译码。

2.2.2.5扩展的输入/输出设备编址扩展的I/O设备地址总线有16条线,A15~A0,可对64K个设备寻址。A15为最高有效位。

2.2.3状态总线

状态总线有八条信号线,它们标志着现行总线周期的特征并指出地址总线上地址的性质。

状态线上信号的助记符号都以小写的s开头。这8条状态信号线是:a.存储器读

b.取指令

e.写周期

f.中断响应

名.暂停响应

五.十六位数据传输请求

SXTRQ*

上述8个信号必须由现行总线主设备产生。所有的状态线均为三态线。

状态总线的有效性见2.7.2。

2.2.3.1状态储存器写

一个相关的状态信号是无法从总线上直接获得的,它由单独的从设备将两个有关号相结合而产生。状态存储器写的定义如下:sMemorywrite=(-sOUT)*sWO(逻辑关系式)亦即,当sOUT为“伪”而sWO为“真”时,状态存储器写为“真”。2.2.3.2状态对照表

表5给出了所有可能的总线周期的状态字定义。8

状态位

周期类型

存储器读

取指令

存储器写

中断响应

暂停应响

空操作

HHHHLLLLL

B-8位操作:

X—任意:

W———16位操作。

2.2.4数据总线

SJ2559-84

表5状态对照表

LLHHLLLLLLXXX

HHHHLLLLHHHHH

LLLLLLHHLLLLL

LLLLLLLLHHLLL

LLLLLLLLLLHHL

LLLLLLLLLLLLH

sXTRQ*

LHLHLHLHLHLX

数据的输入与输出取决于现行总线主设备。现行总线主设备将数据发送给总线从设备叫做数据输出:现行总线主设备接收来自总线从设备的数据叫做数据输入。数据总线共有16条线。它们既可组成两个8位单向总线供字节操作使用,亦可一起作为一个16位双向总线供字操作使用。2.2.4.1字节操作

两个8位单向总线用于字节传输。数据输出使用数据输出总线(DO7DOo),其中DO7为最高有效位。数据输入使用数据输入总线(DI7~DI0)。这里,DI7是最高有效位。

2.2.4.2字操作

DI和DO总线合在一起构成16位双向总线,供16位数据传输之用。16位请求(sXTRQ*)和16位响应(SIXTN*)这两个信号控制着DI和DO的合并,当这两个信号线被激励时(即低态),两个8位总线即实现合并,这时偶地址字节在DO总线【现在改称为ED7~EDo,ED代表“偶数据”(evendata))上,而奇地址字节在DI总线(现在改称为OD7~ODo,OD代表“奇数据”(odddata))上。8位和16位操作协议的完整规定见2.6。2.2.5控制输出总线

5条控制输出总线决定了任一总线周期的时序和数据流动,控制输出信号的信号名9

SJ2559-84

均以小写字母p开始。这5条线是:a.pSYNC表示一个新总线周期的开始。b.PSTVAL*它的有效沿与pSYNC一起标志着在现行总线周期中可以从总线获得稳定的地址和状态。

c.PDBIN广义的读选通信号。它将数据从被访间的从设备读到数据总线上。d.pWR*广义的写选通信号。它将数据总线上的数据写入被访问的从设备。e.PpNLDA占用响应信号。它向最高优先级暂时性主设备表示永久性主设备放弃对总线的控制。

控制输出信号受2.7、3.8和3.9给出的功能与时序的约束。2.2.6控制输人总线

控制输入总线有六条信号线,总线从设备用它来使总线主设备的动作与总线从设备的内部情况(如数据未准备好)同步,并请求永久性主设备操作(如中断或占用操作)。这6条信号线如下:

2.2.6.1准备好信号线

准备好信号线由总线从设备用来同步总线主设备,使其与该从设备的速度合拍。在这种情况下,当前周期中由于被插入等待状态而暂停,直至二者同步为止。RDY信号线对总线从设备来说是通用的,它为集电极开路线。XRDY线是专用准备好线,一般由前面板设备用来停止和单步总线主设备。XRDY规定为有源线,由于可能存在总线冲突,因此它不应被其它总线从设备使用。2.2.6.2中断信号线

中断信号线有两条-INT*和NMI*,用来向永久性总线主设备请求服务,INT*信号通常可以由总线主设备用内部软件操作的方式将其屏蔽。如果主设备接受INT*线上的中断请求,那么它可以产生一个中断响应总线周期来从数据总线接收中断向量。在向量中断期间,INT*表示向量中断控制器接受一个或多个向量中断请求。NMI*信号线为非屏蔽中断请求线,亦即它不可被总线主设备所屏蔽。接受NMI*储号线上的中断请求不必产生中断响应总线周期。INT*线上的中断请求信号是电平信号,它一直保持至接收到中断服务为止。NMI线上的中断请求信号为一个负跳变,因为它不须产生中断响应周期。这两条线均为集电极开路线。

2.2.6.3占用请求

SJ2559-84

暂时性总线主设备向永久性总线主设备请求获得总线控制时使用占用请求信号HOLD*。HOLD*信号线可被永久性总线主设备屏蔽,使暂时性总线主设备不能获得对总线的控制。HOLD*信号线规定为集电极开路线,并只可在规定的时间建立,见2.8.3。

2.2.6.416位响应

16位响应信号SIXTN*是对状态信号“16位请求”(sXTRQ*)的回答,它表示可以进行所要求的16位数据传输。SIXTN*信号线规定为集电极开路线。使用该信号的详细规定见2.6。2.2.7TMA控制总线免费标准下载网bzxz

TMA控制总线有8条信号线,它们与控制总线信号HOLD*和pHLDA相配合用来对多个暂时性主设备同时提出的总线控制请求进行仲裁并禁止永久性总线主设备的信号驱动器,从而按一定顺序完成总线控制的转移。TMA控制总线的8条信号线全部规定为集电极开路线,它们是

使用这8个信号的详细规定见2.8。2.2.7.1TMA仲裁

对多个暂时性主设备提出的总线控制请求进行仲裁的是TMA0*~TMA3*四条信号线,请求者的优先级编码置于这四条线上,稳定后,只有最高优先级设备的优先数被保留。

这一过程的详细规定见2.8.3。

2.2.7.2总线转移信号

TMA控制总线上有四个信号供禁止永久性总线主设备的信号驱动器之用。它们是:

地址禁止

b.DODSB*数据输出禁止

状态禁止

控制输出禁止

注:在8位传输过程中(sXTRQ*无效),DODSB*信号必须禁止八个DO总线驱动器(DOT和DOO)在11

S-100总线规范

1984-12-25发布

中华人民共和国电子工业部

1985-10-01实施

1总述

1.1范围

中华人民共和国电子工业部部标准S-100总线规范

本标准适用于通过S一100总线进行互连的计算机系统部件的接口系统。SJ2559-84

凡具备下列条件的微处理器计算机系统或系统中的若干部分,均在本标准适用范围之内。

a,互连设备之间交换的数据为数字量。b,互连设备的总数最多为22个。c.互连设备之间的传输路径总长度小于或等于63.5cm(25in)。d.总线上任何信号的最大转换速率小于等于6MHz。1.2目的

本标准育在:

a.为新计算机系统部件的设计人员定义一种合理的、通用的接口系统,从而保证S-100总线计算机系统无论在目前还是将来都能够兼容。b,为微处理器计算机系统的用户提供兼容的设备系列,这些设备无须改动便可以明确无误的方式进行通信,并可构成以模块方式扩充的计算机系统。c,使不同厂家生产的设备可互连成一个系统。d.规定与本总线系统有关的术语和定义。e.定义一种系统,该系统对与之相连接的设备的性能特性限制最少。f.定义一种价格相对较低的系统,并允许廉价设备互连。g.定义种容易使用的系统。

1.3定义

下列定义仅用于本标准。本条只给出一般定义,详细定义在其它相应条款中给出。1.3.1一般系统术语

1.3.1.1兼容性(compatibility):按本标准2、3、4章进行设计时,设备无修改即可互连和使用的程度。

1.3.1.2设备(device):在一块或多块插件板上的一个电路或多个电路的逻辑组合,它们通过总线可以与其它符合本定义的设备相互作用。1.3.1.3接口(interface):计算机系统各部分之间共享的电气界面。信息通过它进行传输。

电子工业部1984-12-02发布

1985-10-01实施

SJ2559-84

1.3.1.4接口系统(interfacesystem):在-组设备间实现明确无误的通信所必须的、独立于设备的功能、电气和机械接口要素。典型的接口系统要素有:驱动器与接收器电路、信号线描述、时序与控制规约、数据传输协议和功能逻辑电路等。1.3.1.5K字节(kilobyte):1024=2101.3.1.6M字节(megabyte):1048576=221.3.1.7系统(system):一套相互关联的部件,它迹过执行规定的功能来实现给定的目的。

1.3.2信号与通路

1.3.2.1有效(active):信号处于逻辑值为“真”的状态。1.3.2.2激励(activate):同“建立”(assert)。1.3.2.3建立(assert):使信号线从逻辑“伪”(无效)状态转变成逻辑“真(有效)状态。“真”取有效状态可以是高态也可以是低态,每一信号均有具体规定。1.3.2.4双向总线(bidirectionalbus):为单个设备或套设备使用的、具有输入和输出两种数据传输方式的总线。1.3.2.5位并行(bit-parallel):用来载递信息的、同时存在于同样数量信号线上的一组数据位。这些位并行数据位可一起用作一个整体,也可以用作独立的数据位。

1.3.2.6总线(bus):接口系统所使用的一组信号线。设备通过它相互连接和传递信息。

1.3.2.7总线周期(buscycle):实现总线数据传输所需的电脉冲基本序列。一个总线周期必须包括至少三个总线状态。1.3.2.8总线状态(busstate):一个总线状态的持续时间为一个时钟周期。它的开始和结束恰好处于系统时钟中的上升沿之前。每一个总线周期中必须至少有三个总线状态。

1.3.2.9字节(byte):组作为整体看待的,对应于二进制数字的位并行信号,它由八个二进制位构成。其最高有效位脚标为7,最低有效位脚标为0。1.3.2.10字节串(byte-serial):经公共总线载递信息的位并行数据字节序列。

1.3.2.11撤消(deactivate):使信号由逻辑“真”(有效)状态转变成逻辑“伪”(无效)状态,它是“建立”的逆操作。1.3.2.12高态(highstate):用来建立某种特定消息内容的较高的正信号电平。这一特定消息内容仅由两个二进制逻辑状态之一表征。1.3.2.13无效(inactive):信号处于逻辑伪”状态。1.3.2.14低态(1owstate):用来表征某种特定消息的较低的正信号电平,这一特定消息仅由两个二进制逻辑状态之一表征。2

SJ2559-84

1),数据从一点传递到另一点的物理表示。在本标准范围1.3.2.15信号(signal

内,信号仅指数字电信号。

1.3.2.16信号电平(signallevel):相对于任一选定的参考量(本标准中为电压)的信号量值。

1.3.2.17信号线(signalline):接口系统中用来在互连设备之间传送消息的组信号导体之。

1.3.2.18信号参数(signalparameter):一种电量参数,其值或值的序列用来传递信息。

1.3.2.19单向总线(unidirectionalbus):设备用来单向传送消息的总线,它或者只能输出或者只能输入。

1.3.2.20字(word):一组作为整体看待的对应于二进制数字的位并行信号。本标准中一个字为16位,其最高有效位的脚标为15,最低有效位的脚标为0。1.4状态图表示法

将一种接口功能能够出现的每一种状态用一个圆圈表示,圆圈内标上助记符作为该状态的标志。这些状态之间合法的转换在它们之间用箭头表示。状态之间每一转换可用~表达式描述,该表达式的值非“真”即“伪”只具其一,如图所示。没有表达式描述的状态转换意味着该转换将发生在一定的时间间隔之后,正如时序规范中所指明的那样。当且仅当输入(driving)表达式值为“真”,或在时间相关的转换情况下,接口功能应在最小规定时间过后立即进入指定状态。爽达式1

表达式2

状态图表示法

一个表达式由输入(driving)表达式和输出(driven)表达式两部分组成,中间用斜杠(/)隔开。输入表达式必须给出状态转换所需的条件。输出表达式是可选的,用来表示作为状态转换结果的信号转换。信号转换的表示为:信号名后跟等号,然后是状态助记符,这个状态是作为转换结果的信号所处的状态。输入表达式由一条或多条消息用运算符连结而成。这些运算符是:AND(a·b),OR(a+b)和NOT(a)。优先级用括号规定。下面为一表达式的例子:(输入/输出)A·(B+C)/D=F(ALSE),E=T(RUE)如果“A与(B或C)”为“真”,则D被强置为\伪”而E被强置为“真”,并发生状3

态转换。

SJ2559-84

1.5逻辑状态与电气状态的关系

本标准对信号的逻辑功能与它的电气实现做了区分。在本标准中,所有的等式均为逻辑关系式而不是电气关系式(除非另有说明),并按逻辑状态写出。表1和表2给出了逻辑状态的两种电气实现形式。表1

高有效信号

高有效信号由信号名助记符后面不加任何后级表示(如ABCD)逻辑状态

伪(F)

真(T)

二进制状态

信号电平

≤08V,称为低态

>2.0V,称为高态

表2低有效信号

低有效信号由信号名助记符后跟*号表示(如ABCD*)逻辑状态

伤(F)

真(T)

二进制状态

信号电平

>2.0V,称为高态

<0.8V,称为低态

电气状态

电气状态

在进行逻辑关系式的电气实现时,必须注意说明电信号的特性是高有效还是低有效。例如,逻辑等式为:

MWRT=pWR*-sOUT

在电气实现时则为:

(逻辑关系式)

MWRT=(-pWR*)*-sOUT(电气关系式)这是因为:pWR*表示总线上载有pWR信息的电信号.事实上,上式与MWRT=-(pWS+sOUT)(电气关系式)是相同的。因此,根据德摩根(deMorgan)定理,只须一个满足加载与驱动条件的双输入或非门就完全可以实现MWRT。信号电平的边沿或变化在时序图中给出。当逻辑变量值由“伪”变成“真”时相应的信号电平的变化或边沿为:

高有效

低有效

SJ2559-84

状态图中的状态关系式均按逻辑状态给出而不用电气状态。作为后缀的星号*并不是否定运算符,它只是一个与信号名相连的标志符(如同一个注释或脚注),用来表示逻辑状态与电气状态之间的关系。就是说,当信号线呈现低电平时该变量是“真”值。前缀负号“”为逻辑否定运算符,它与上横线的意义相同。为清楚起见,在必要时可用括号标出否定的范围。

1.6接口系统概述

1.6.1接口系统的目的

接口系统总的目的是提供一种高效率的通信链路,通过它,消息能以明晰准确的方式在一组互连设备之间传递。

接口系统中的消息划分为两大类a.用于控制接口系统本身的消息,称作接口消息。b,经接口系统传递且为该系统互连的设备所使用,但又不是接口系统本身的一部份,这种消息称作设备相关消息(如数据)。本标准所描述的接口系统仅包括接口消息的功能与电气规范,对于设备相关消息的特性和意义本标准不作规定。

1.6.2基本通信能力

一个高效率的通信链路须具有两种基本的功能部件,才能对设备之间的信息流实施组织和管理:

a,起总线主设备作用的设备。

b.起总线从设备作用的设备。

总线主设备和总线从设备之间所有的信息传输均由统一化的总线周期实现。该总线周期由总线主设备产生,为被寻址的总线从设备所响应。在本标准所描述的接口系统中,8.总线主设备能够产生完成一个总线周期所必须的全部接口消息,并借此访问全部或部分总线从设备。该主设备可以从被访问的从设备接收或向被访问的从设备发送设备相关消息作为总线周期的一部分。b,总线从设备监视全部总线周期。因此,它能被总线主设备访问并向主设备发送或接收主设备发出的设备相关信息。总线主设备和总线从设备功能既可单独地也可共同地存在于由本标准定义的接口系统所互连的插件板上。

1.6.3消息通路与总线结构

S100总线接口系统由一组信号线构成,这组信号线用来传递互连设备间的全部信息一一接口消息和设备相关消息。S一100总线的结构归结为八组信号线和一组电源线,如表3所示。5

2功能规范

(1)数据总线

(2)地址总线

(3)状态总线

(4)控制输出总线

(5)控制输入总线

(6)TMA控制总线

(7)向量中断总线

SJ2559-84

表3总线结构

(8)其它各种用途总线

(9)电源总线

2.1功能划分

16条信号线

16条或24条信号线

8条信号线

5条信号线

6条信号线

8条信号线

8条信号线

16条信号线

9条电源线

由接口系统互连的设备按产生还是接收接口信息分为两类一一总线主设备和总线从设备。

起总线主设备作用的设备负责形成总线周期并产生为执行正确的总线周期所需的全部信号。这些信号称作M类信号,它们由地址、状态和控制总线信号组成。设备相关消息从数据总线发送和接收。

总线主设备又分为两类:一类为永久性主设备,另一类是暂时性主设备。水久性总线主设备(通常为CPU)是接口系统中具有最高优先级的主设备。暂时性主设备可向永久性主设备请求占用总线任意数量的总线周期,然后将总线控制权交还给永久性总线主设备。总线控制权由永久性主设备交给暂时性主设备然后又返回永久性主设备这一转移过程称为TMA(TemporrymasterAccess)周期。永久性总线主设备和暂时性总线主设备的区别如下:8.接口系统中只能有-个永久性主设备存在,面一个系统中同时存在的暂时性主设备最多可达十六个。

b.暂时性主设备不提供TMA周期,就是说,没有嵌套的TMA操作。起总线从设备作用的设备是总线周期接收者。总线从设备监视所有的总线周期,且在某个特定总线周期中被寻址,便从数据线发送或接收所要求的设备相关消息。总线主设备必须产生规定的一组信号来形成一个正确的总线周期,而总线从设备只需检查和产生那些与总线主设备通信所必须的总线信号子集。2.2信号线

2.2.1概述

对现行总线主设备来说总线是消息通路的集合。它们是:a.地址总线:

b.状态总线:

c.数据输入/输出总线

d.控制输出总线:

e.控制输入总线:

f.TMA控制总线:

g.向量中断总线:

h.其它各种用途总线。

SJ2559-84

每一总线的特性和用途在以下各款中规定。除另有说明外,所有总线信号线均为三态线。

2.2.2地址总线

地址总线由16或24条位并行信号线组成,为现行总线周期中的通信提供具体的存储单元或输入/输出设备的地址。

所有的总线主设备必须建立A0至A15地址位,而A16至A23则可根据需要作为扩充使用。

地址总线的有效性在2.了.2中定义。地址线全部为三态线。

表4概括了各种总线周期所使用的地址。表4不同总线周期的地址使用

周期类型

存储器读

存储器写

M1(取指周期)

中断响应

暂停响应

标推编址

A15~A0

A7~A0

注:输入输出的标准编址见2.2.2.4。2.2.2.1标准存储器编址

扩展编址

A23~A0

A15~A0

标准存储器地址总线由16条线构成,寻址能力达64K字节存储单元。这16条线顺序记为A15~A0,A15为最高有效位。2.2.2.2扩展存储器编址

扩展的存储器地址总线由24条线组成,可对16M字节的存储单元进行导址。这24条线记为A23~A0,其中A23为最高有效位。7

2.2.2.3PHANTOM*

SJ2559-84

PHANTOM*信号提供了以一个公共地址单元覆盖两个存储器从设备的能力。当PHANTOM*信号线被激励时,影象(Phantom)存储器从设备有效而常规(norm-al)存储器无效。在PHANTOM*信号建立时,所有的常规存储器从设备必须能被禁止。在读和写周期出现PHANTOM*信号时也必须将常规存储器禁止。2.2.2.4标准输入/输出设备编址标准I/O设备地址总线有8条线,A7~A0,可对256个I/O设备编址。A7为最高有效位。

注:I/O设备地址习惯上总放在高序地址字节A15~A8.鼠然这一增尴是可以接受的,但是并不推荐在新的设计中采用,因为它使扩膳的I/O设备编址复杂化了。标准I/O从设备决不应只做靠对高序地证学节译码。

2.2.2.5扩展的输入/输出设备编址扩展的I/O设备地址总线有16条线,A15~A0,可对64K个设备寻址。A15为最高有效位。

2.2.3状态总线

状态总线有八条信号线,它们标志着现行总线周期的特征并指出地址总线上地址的性质。

状态线上信号的助记符号都以小写的s开头。这8条状态信号线是:a.存储器读

b.取指令

e.写周期

f.中断响应

名.暂停响应

五.十六位数据传输请求

SXTRQ*

上述8个信号必须由现行总线主设备产生。所有的状态线均为三态线。

状态总线的有效性见2.7.2。

2.2.3.1状态储存器写

一个相关的状态信号是无法从总线上直接获得的,它由单独的从设备将两个有关号相结合而产生。状态存储器写的定义如下:sMemorywrite=(-sOUT)*sWO(逻辑关系式)亦即,当sOUT为“伪”而sWO为“真”时,状态存储器写为“真”。2.2.3.2状态对照表

表5给出了所有可能的总线周期的状态字定义。8

状态位

周期类型

存储器读

取指令

存储器写

中断响应

暂停应响

空操作

HHHHLLLLL

B-8位操作:

X—任意:

W———16位操作。

2.2.4数据总线

SJ2559-84

表5状态对照表

LLHHLLLLLLXXX

HHHHLLLLHHHHH

LLLLLLHHLLLLL

LLLLLLLLHHLLL

LLLLLLLLLLHHL

LLLLLLLLLLLLH

sXTRQ*

LHLHLHLHLHLX

数据的输入与输出取决于现行总线主设备。现行总线主设备将数据发送给总线从设备叫做数据输出:现行总线主设备接收来自总线从设备的数据叫做数据输入。数据总线共有16条线。它们既可组成两个8位单向总线供字节操作使用,亦可一起作为一个16位双向总线供字操作使用。2.2.4.1字节操作

两个8位单向总线用于字节传输。数据输出使用数据输出总线(DO7DOo),其中DO7为最高有效位。数据输入使用数据输入总线(DI7~DI0)。这里,DI7是最高有效位。

2.2.4.2字操作

DI和DO总线合在一起构成16位双向总线,供16位数据传输之用。16位请求(sXTRQ*)和16位响应(SIXTN*)这两个信号控制着DI和DO的合并,当这两个信号线被激励时(即低态),两个8位总线即实现合并,这时偶地址字节在DO总线【现在改称为ED7~EDo,ED代表“偶数据”(evendata))上,而奇地址字节在DI总线(现在改称为OD7~ODo,OD代表“奇数据”(odddata))上。8位和16位操作协议的完整规定见2.6。2.2.5控制输出总线

5条控制输出总线决定了任一总线周期的时序和数据流动,控制输出信号的信号名9

SJ2559-84

均以小写字母p开始。这5条线是:a.pSYNC表示一个新总线周期的开始。b.PSTVAL*它的有效沿与pSYNC一起标志着在现行总线周期中可以从总线获得稳定的地址和状态。

c.PDBIN广义的读选通信号。它将数据从被访间的从设备读到数据总线上。d.pWR*广义的写选通信号。它将数据总线上的数据写入被访问的从设备。e.PpNLDA占用响应信号。它向最高优先级暂时性主设备表示永久性主设备放弃对总线的控制。

控制输出信号受2.7、3.8和3.9给出的功能与时序的约束。2.2.6控制输人总线

控制输入总线有六条信号线,总线从设备用它来使总线主设备的动作与总线从设备的内部情况(如数据未准备好)同步,并请求永久性主设备操作(如中断或占用操作)。这6条信号线如下:

2.2.6.1准备好信号线

准备好信号线由总线从设备用来同步总线主设备,使其与该从设备的速度合拍。在这种情况下,当前周期中由于被插入等待状态而暂停,直至二者同步为止。RDY信号线对总线从设备来说是通用的,它为集电极开路线。XRDY线是专用准备好线,一般由前面板设备用来停止和单步总线主设备。XRDY规定为有源线,由于可能存在总线冲突,因此它不应被其它总线从设备使用。2.2.6.2中断信号线

中断信号线有两条-INT*和NMI*,用来向永久性总线主设备请求服务,INT*信号通常可以由总线主设备用内部软件操作的方式将其屏蔽。如果主设备接受INT*线上的中断请求,那么它可以产生一个中断响应总线周期来从数据总线接收中断向量。在向量中断期间,INT*表示向量中断控制器接受一个或多个向量中断请求。NMI*信号线为非屏蔽中断请求线,亦即它不可被总线主设备所屏蔽。接受NMI*储号线上的中断请求不必产生中断响应总线周期。INT*线上的中断请求信号是电平信号,它一直保持至接收到中断服务为止。NMI线上的中断请求信号为一个负跳变,因为它不须产生中断响应周期。这两条线均为集电极开路线。

2.2.6.3占用请求

SJ2559-84

暂时性总线主设备向永久性总线主设备请求获得总线控制时使用占用请求信号HOLD*。HOLD*信号线可被永久性总线主设备屏蔽,使暂时性总线主设备不能获得对总线的控制。HOLD*信号线规定为集电极开路线,并只可在规定的时间建立,见2.8.3。

2.2.6.416位响应

16位响应信号SIXTN*是对状态信号“16位请求”(sXTRQ*)的回答,它表示可以进行所要求的16位数据传输。SIXTN*信号线规定为集电极开路线。使用该信号的详细规定见2.6。2.2.7TMA控制总线免费标准下载网bzxz

TMA控制总线有8条信号线,它们与控制总线信号HOLD*和pHLDA相配合用来对多个暂时性主设备同时提出的总线控制请求进行仲裁并禁止永久性总线主设备的信号驱动器,从而按一定顺序完成总线控制的转移。TMA控制总线的8条信号线全部规定为集电极开路线,它们是

使用这8个信号的详细规定见2.8。2.2.7.1TMA仲裁

对多个暂时性主设备提出的总线控制请求进行仲裁的是TMA0*~TMA3*四条信号线,请求者的优先级编码置于这四条线上,稳定后,只有最高优先级设备的优先数被保留。

这一过程的详细规定见2.8.3。

2.2.7.2总线转移信号

TMA控制总线上有四个信号供禁止永久性总线主设备的信号驱动器之用。它们是:

地址禁止

b.DODSB*数据输出禁止

状态禁止

控制输出禁止

注:在8位传输过程中(sXTRQ*无效),DODSB*信号必须禁止八个DO总线驱动器(DOT和DOO)在11

小提示:此标准内容仅展示完整标准里的部分截取内容,若需要完整标准请到上方自行免费下载完整标准文档。

标准图片预览:

- 其它标准

- 热门标准

- 电子行业标准(SJ)

- SJ/T31450-1994 氧气输送管道完好要求和检查评定方法

- SJ/T11376-2007 数字电视接收设备条件接受接口规范 第2-1部分:通用传送接口(UTI)技术规范

- SJ/T31449-1994 供油管道完好要求和检查评定方法

- SJ/T11138-1997 电缆分配系统用物理发泡聚乙烯绝缘同轴电缆

- SJ/T10148.1-1991 电气简图的编制方法 术语、分类和编制原则

- SJ/T11399-2009 半导体发光二极管芯片测试方法

- SJ/T11403-2009 通信用激光二极管模块可靠性评定方法

- SJ/Z610-73 场致发光荧光粉的试验方法

- SJ/T11377-2007 数字电视接收设备条件接受接口规范 第2-2部分:通用传送接口(UTI)测试规范

- SJ50033.129-1997 半导体分立器件 3DD155型低频大功率晶体管详细规范

- SJ/T31452-1994 水处理设备完好要求和检查评定方法

- SJ/T10795-1996 通用硬同轴传输线及其法兰连接器详细规范

- SJ20978.3-2007 空中交通管制系统监视数据交换规范第3部分:单雷达气象信息传输

- SJ3062.2-1988 冲裁模通用模架 T形槽固定板

- SL/T809—2021 水利对象基础数据库表结构及标识符

- 行业新闻

请牢记:“bzxz.net”即是“标准下载”四个汉字汉语拼音首字母与国际顶级域名“.net”的组合。 ©2025 标准下载网 www.bzxz.net 本站邮件:wymp4wang@gmail.com